ОўРНјЖЛг»ъөДЧйіЙ

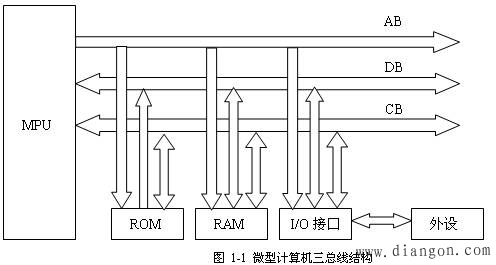

ОўРНјЖЛг»ъТФОўҙҰАнЖчОӘәЛРДЈ¬ЖдТ»ҙуМШөгКЗІЙУГЧЬПЯҪб№№Ј¬ЖдЦРИэЧЬПЯҪб№№УИОӘЖХұйЈ¬ИзНј1-1ЛщКҫЎЈMPUЈЁОўҙҰАнЖчЈ©КЗНЁ№эABЈЁөШЦ·ЧЬПЯЈ©ЎўDBЈЁКэҫЭЧЬПЯЈ©әНCBЈЁҝШЦЖЧЬПЯЈ©ХвИэЧЬПЯУлROMЈЁЦ»¶БҙжҙўЖчЈ©әНRAMЈЁЛж»ъҙжҙўЖчЈ©ј°I/OЈЁКдИл/КдіцЈ©ҪУҝЪПаБ¬өДЎЈФЪ·ЦОцОўРНјЖЛг»ъ»щұҫ№ӨЧчФӯАнЗ°Ј¬ПИ¶ФёчІҝјюҪшРРҪйЙЬЎЈ1Ј®ҙжҙўЖч

ҙжҙўЖчУЦіЖДЪҙж»тЦчҙжЈ¬КЗјЖЛг»ъөДҙжҙўІҝјюЈ¬УГАҙҙж·ЕіМРтәНКэҫЭ(ФӯКјКэҫЭЎўЦРјдҪб№ыј°ЧоәуҪб№ы)ЎЈОўРНјЖЛг»ъДЪҙжУЙ°лөјМеҙжҙўЖчROMәНRAMЧйіЙЈ¬ЛьГЗ¶јКЗІЙУГҙу№жДЈ»ті¬ҙу№жДЈјҜіЙөзВ·№ӨТХЦЖіЙөДҙжҙўЖчРҫЖ¬Ј¬ҫЯУРМе»эРЎЎўЦШБҝЗбЎўјҜіЙ¶ИёЯөИМШөгЎЈ

Ц»¶БҙжҙўЖчROMЈЁRead Only MemoryЈ©КЗТ»ЦЦФЪХэіЈ№ӨЧчКұЦ»¶БІ»ДЬРҙөДҙжҙўЖчЈ¬АыУГМШКвКЦ¶ОҪ«№М¶ЁіМРтәНіЈКэРҙИлROMЈ¬Т»ө©РҙИлұгДЬіӨЖЪұЈҙж(¶ПөзТІІ»¶ӘК§)Ј¬РиТӘКұјҙҝЙ¶БіцК№УГЎЈROMНЁіЈУГАҙҙж·ЕІ»ұдөДіМРтЈ¬Из»щұҫI/OіМРтЎўјаҝШіМРтЎў»гұаіМРтЎўёЯј¶УпСФ/ҪвКНіМРтөИЈ¬»№ҙжҙўёчЦЦіЈУГКэҫЭәНұнёсЎЈROMөДЦЦАаәЬ¶аЈ¬°ҙХХұаіМ·ҪКҪЈ¬Ц»¶БҙжҙўЖчROM·ЦОӘСЪДЈROMЎўҝЙұаіМROMЎўҝЙІБіэEPROMЎўөзІБіэE2PROMәНЙБЛЩҙжҙўЖчFlash PEROMЎЈFlash PEROMҝЙТФФЪПЯРҙИлЈЁЧФ¶ҜІБіэЈ©Ј¬ІўЗТҝЙТФ°ҙТіБ¬РшЧЦҪЪРҙИлЈ¬¶БіцЛЩ¶ИТІәЬҝмЎЈ

Лж»ъҙжИЎҙжҙўЖчRAMЈЁRandom Access MemoryЈ©КЗТ»ЦЦФЪХэіЈ№ӨЧчКұјИДЬ¶БУЦДЬРҙөДҙжҙўЖчЈ®УГАҙҙж·ЕУГ»§ТӘФЛРРөДіМРтј°ФЛРРіМРтЛщРиөДФӯКјКэҫЭЎўЦРјдҪб№ыЎўЧоЦХҪб№ыТФј°КөКұКэҫЭөИЎЈRAMЦРҙжҙўөДРЕПўІ»ДЬіӨҫГұЈҙжЈ¬НЈөзәуұгБўјҙПыК§Ј¬ТтҙЛУЦіЖОӘТЧК§РФ»тТЧ»У·ўРФҙжҙўЖчЎЈRAMҙжҙўЖчөД№жёсЖ·ЦЦТІәЬ¶аЈ¬Из4KBЎў8KBЎў32KBЎў64KBЎў256KSBЎўl MBөИөИЎЈ°ҙХХҙжҙўөзВ·өДІ»Н¬Ј¬Лж»ъҙжИЎҙжҙўЖчRAMУЦҝЙ·ЦОӘ¶ҜМ¬RAMЈЁDRAMЈ©ЎўҫІМ¬RAMЈЁSRAMЈ©ЎЈDRAMРҫЖ¬ТФMOS№ЬХӨј«өзИЭКЗ·сідУРөзәЙАҙҙжҙўВЯјӯ1»т0РЕПўЈ¬РиТӘНвҪУЛўРВөзВ·АҙЦЬЖЪРФөШ¶ФЖдөзәЙҪшРРЛўРВТФО¬іЦЛьЛщҙъұнөДКэҫЭЎЈSRAMРҫЖ¬ТФҙҘ·ўЖчАҙҙжҙўВЯјӯ1»т0РЕПўЈ¬ОЮРиЛўРВөзВ·ЎЈSRAMұИDRAMјҜіЙ¶ИөНЎўіЙұҫёЯЎўЛЩ¶ИҝмЎЈSRAMәНDRAMҫщОӘТЧК§РФҙжҙўЖчЎЈ

ROMәНRAMөДЦчТӘЗшұрФЪУЪЈәТ»КЗ¶ПөзәуROMДЪөДРЕПўІ»¶ӘК§Ј¬¶шRAMЦРөДРЕПўБўјҙПыК§Ј»¶юКЗ¶БЈҜРҙ·ҪКҪІ»Н¬Ј¬ROMІЙУГМШКв·ҪКҪРҙИлРЕПўЈ¬РЕПўРҙИләуЦ»ДЬ¶БЈ¬¶шRAMјИДЬ¶БУЦДЬРҙЎЈ

ROMәНRAMҙжҙўЖчРҫЖ¬ЙПөДТэПЯНЁіЈ·ЦОӘЛДЧйЈәөШЦ·ПЯУГУЪПтҙжҙўЖчКдЛНөШЦ·ВлЈ»КэҫЭПЯКЗЛ«ПтөДЈ¬ҙ«ЛН¶ФРҫЖ¬ЦРДіТ»өҘФӘҪшРР¶БЈҜРҙІЩЧчөДКэҫЭЈ»ҝШЦЖПЯУГУЪҙ«ЛНҝШЦЖРЕәЕЈ¬ҝШЦЖІЩЧчКЗҪшРР¶Б»№КЗҪшРРРҙөИөИЈ»өзФҙПЯ№©ёшРҫЖ¬Ј«5VЦұБчөзФҙЎЈЖдЦРөШЦ·ПЯј°КэҫЭПЯөДТэҪЕКэУлРҫЖ¬өДҙжҙўИЭБҝУР№ШЎЈ

өШЦ·ПЯФҪ¶аЈ¬ҙжҙўИЭБҝҫНФҪҙуЈ»КэҫЭПЯФҪ¶аЈ¬ГҝёцөҘФӘЦРҙжҙўөД¶юҪшЦЖКэөДО»КэҫНФҪіӨЎЈАэИзЈ¬өШЦ·ПЯОӘnМхөДҙжҙўЖчРҫЖ¬өДҙжҙўИЭБҝОӘ ёцөҘФӘЈ¬КэҫЭПЯөДМхКэmОӘГҝёцөҘФӘДЬҙжҙўөД¶юҪшЦЖКэөДО»КэЈ¬ФтҙжҙўЖчРҫЖ¬өДҙжҙўИЭБҝОӘ2nЎБmbitЈ¬јҙЈә

ҙжҙўИЭБҝ=2өШЦ·ПЯөДМхКэЎБКэҫЭПЯөДМхКэЈЁbitЈ©

ИзТ»ёцҙжҙўЖчУР16МхөШЦ·ПЯәН8МхКэҫЭПЯЈ¬ЛьөД16О»өШЦ·ҝЙөГөҪ216ёцөШЦ·ұаВлЈ¬ҝЙС°Ц·216ёцөҘФӘЈ¬јҙҙжҙўИЭБҝОӘ216ёцөҘФӘЈ¬ГҝёцөҘФӘ8О»Ј¬ФтҙжҙўИЭБҝОӘ216ЎБ8bitЎЈ

2Ј®ОўҙҰАнЖчЈЁMPUЈ©

ОўҙҰАнЖчMPUКЗОўРНјЖЛг»ъөДФЛЛгәНЦё»УҝШЦЖЦРРДЈ¬ЖдРФДЬҫц¶ЁБЛОўРНјЖЛг»ъөДРФДЬЎЈЛдИ»ёчЦЦОўҙҰАнЖчРФДЬәНДЪІҝҪб№№УРІоТмЈ¬ЦёБоПөНіТІІ»Н¬Ј¬ө«ЛьГЗөД»щұҫЧйіЙПаН¬Ј¬¶ј°ьә¬УРҝШЦЖЖчЎўФЛЛгЖчәНДЪІҝЧЬПЯЎЈОўҙҰАнЖчУлҙжҙўЖчЦ®јдөДҪб№№ҝЙІОХХНј1-2ЎЈ

ЈЁ1Ј©ФЛЛгЖч

ФЛЛгЖчФЪҝШЦЖЖчөДҝШЦЖПВ¶Ф¶юҪшЦЖКэҪшРРЛгКхФЛЛг»тВЯјӯІЩЧчЎЈФЛЛгЖчУЙЛгКхВЯјӯөҘФӘЙҫЎўАЫјУЖчAЎўНЁУГјДҙжЖчPSЎўФЭҙжЖчTMPәНіМРтЧҙМ¬ЧЦPSWөИОеІҝ·ЦЧйіЙЎЈ

ўЩЛгКхВЯјӯөҘФӘALUЈә ALUКЗФЛЛгЖчөДәЛРДЈ¬ЛьТФИ«јУЖчОӘ»щҙЎЈ¬ІўёЁТФТЖО»әНҝШЦЖВЯјӯЧйәП¶шіЙЈ¬ФЪҝШЦЖРЕәЕөДҝШЦЖПВЈ¬ҝЙҪшРРјУјхіЛіэөИЛгКхФЛЛгәНёчЦЦВЯјӯФЛЛгЎЈ

ўЪАЫјУЖчAЈәAКЗУЙҙҘ·ўЖчЧйіЙөДТЖО»јДҙжЖчЈ¬ФЪФЛЛгЗ°ҙж·ЕТ»ёцІЩЧчКэЈ¬ФЛЛгәуҙж·ЕФЛЛгҪб№ыЎЈ

ўЫФЭҙжЖчTMPЈәTMPТІКЗТ»ёцјДҙжЖчЈ¬УГУЪФЭҙжБнТ»ІЩЧчКэЎЈ

ўЬіМРтЧҙМ¬ЧЦPSWЈәPSWУЙ8О»ҙҘ·ўЖчЧйіЙЈ¬ҙж·ЕALUІЩЧч№эіМЦРРОіЙөДЧҙМ¬ЎЈАэИзЈәАЫјУЖчAЦРөДФЛЛгҪб№ыКЗ·сОӘБгЈ¬ЧоёЯО»КЗ·сУРҪшО»»тҪиО»Ј¬өН4О»ПтёЯ4О»КЗ·сУРҪшО»»тҪиО»өИөИЈ¬¶јФЪPSWЦРПаУҰО»ЙПҪшРРұкЦҫЎЈ

ўЭНЁУГјДҙжЖчPSЈәPSУГУЪҙж·ЕІЩЧчКэ»тФЛЛгҪб№ыЎЈ

ФЪФЛЛгЗ°Ј¬Ҫ«ФЛЛгЛщРиІЩЧчКэЛНИлАЫјУЖчәНФЭҙжЖчЈ¬УЙҝШЦЖРЕәЕҝШЦЖALUҪшРРФЛЛгЈ¬°СФЛЛгҪб№ыҙж·ЕөҪАЫјУЖчAЈ¬ІўёщҫЭФЛЛгҪб№ыЙиЦГіМРтЧҙМ¬ЧЦPSWЧҙМ¬О»өДЦөЎЈ

ЈЁ2Ј©ҝШЦЖЖч

ҝШЦЖЖчКЗ·ўІјІЩЧчГьБоөД»ъ№№Ј¬КЗјЖЛг»ъөДЦё»УЦРРДЈ¬ПаөұУЪИЛДФөДЙсҫӯЦРКаЈ¬ҝШЦЖјЖЛг»ъөДёчІҝ·ЦРӯөч№ӨЧчЈ¬УГУЪЧФ¶ҜЦҙРРіМРтЎЈҝШЦЖЖчУЙЦёБоІҝјюЎўКұРтІҝјюәНОўІЩЧчҝШЦЖІҝјюөИИэІҝ·ЦЧйіЙЎЈ

ўЩЦёБоІҝјюЈәЦёБоІҝјюКЗУГАҙ¶БИЎЦёБоЎў·ЦОцЦёБоәНОӘНкіЙЦёБоІъЙъҝШЦЖРЕәЕөДВЯјӯІҝјюЈ¬ТІКЗҝШЦЖЖчөДәЛРДЎЈНЁіЈЈ¬ЦёБоІҝјюУЙіМРтјЖКэЖчPCЎўЦёБојДҙжЖчIRәНЦёБоТлВлЖчIDөИИэІҝ·ЦЧйіЙЎЈ

ўЪКұРтІҝјюЈәКұРтІҝјюУЙКұЦУПөНіәНВціе·ЦЕдЖчЧйіЙЈ¬УГУЪІъЙъОўІЩЧчҝШЦЖІҝјюЛщРиөД¶ЁКұВціеРЕәЕЎЈКұЦУПөНіІъЙъ»ъЖчөДКұЦУВціеРтБРЈ¬Вціе·ЦЕдЖчУЦіЖҪЪЕД·ўЙъЖчЈ¬УГУЪІъЙъҪЪЕДөзО»әНҪЪЕДВціеЎЈ

ўЫОўІЩЧчҝШЦЖІҝјю ОўІЩЧчҝШЦЖІҝјюОӘЦёБоТлВлЖчmөДКдіцРЕәЕЕдЙПҪЪЕДөзО»әНҪЪЕДВціеЈ¬ТІҝЙәННвІҝҪшАҙөДҝШЦЖРЕәЕЧйәПЈ¬№ІН¬РОіЙПаУҰөДОўІЩЧчҝШЦЖРтБРЈ¬ТФНкіЙ№ж¶ЁөДІЩЧчЎЈ

јЖЛг»ъөД№ӨЧчҫНКЗЦҙРРіМРтЎЈТӘЦҙРРТ»ёціМРтұШРлҪ«ёГіМРт·ЕИлДЪҙжЈ¬¶шіМРтКЗИфёЙЦёБоөДУРРтЕЕБРЈ¬ТӘЦҙРРіМРтЦ»ТӘҙУөЪТ»МхЦёБоҝӘКјЈ¬ЦрМх¶БИЎЦёБоЎў·ЦОцЦёБоЎўЦҙРРЦёБоЦұЦБЦҙРРөҪНЈ»ъЦёБојҙНкіЙіМРтЎЈТӘҙУДЪҙжЦР¶БИЎЦёБоЈ¬ұШРлёшіцДЪҙжөҘФӘөДөШЦ·Ј¬ХвҫНРиТӘУРТ»ёцЧЁГЕөДјДҙжЖчУГАҙҙж·ЕҪ«ТӘЦҙРРЦёБоөДДЪҙжөШЦ·Ј¬ХвёцјДҙжЖчҫНКЗіМРтјЖКэЖчPCЎЈөұјЖЛг»ъёщҫЭPCЦРөШЦ·ИЎіцТӘЦҙРРЦёБоөДТ»ёцЧЦҪЪәуЈ¬PCҫНЧФ¶ҜјУ1Ј¬ЦёПтЦёБоөДПВТ»ЧЦҪЪЈ¬ОӘ»ъЖчПВҙО¶БИЎЦёБоЧцәГЧјұёЎЈ

ЦёБојДҙжЖчIRУГАҙҙж·ЕҙУҙжҙўЖчЦРИЎіцөДөұЗ°ТӘЦҙРРЦёБоөДЦёБоВлЎЈёГЦёБоВлФЪIRЦРөГөҪјДҙжәН»әіеәуұ»ЛНөҪЦёБоТлВлЖчIDЦРТлВлЈ¬ҫӯТлВләуҫНЦӘөАёГЦёБоЛщТӘҪшРРөДІЩЧчЈ¬ІўФЪКұРтІҝјюәНОўІЩЧчҝШЦЖІҝјюөДЧчУГПВҝШЦЖПаУҰІҝјюҪшРРІЩЧчЈ¬ЦҙРРЦёБоЎЈ

3Ј®I/OҪУҝЪәННвЙи

I/OҪУҝЪКЗјЬЙиФЪОўҙҰАнЖчәННвЙијдөДЗЕБәЈ¬КЗТ»ЦЦ№э¶ЙөДҙу№жДЈјҜіЙөзВ·РҫЖ¬ЎЈУЙУЪҙу¶аКэНвЙи¶јКЗ»ъөзРНөДЈ¬№ӨЧчЛЩ¶ИҪПВэЈ¬ТтҙЛОўҙҰАнЖчMPUНЁіЈІ»ДЬәНЛьГЗЦұҪУПаБ¬Ј¬¶шКЗНЁ№эI/OҪУҝЪәННвЙиПаБ¬Ј¬ТФұгКөПЦЛЩ¶ИЎўөзЖҪәНРЕәЕРФЦКөДЖҘЕдЎЈ

4Ј®өШЦ·ЧЬПЯЎўКэҫЭЧЬПЯәНҝШЦЖЧЬПЯ

ЧЬПЯКЗФЪОўРНјЖЛг»ъёчІҝ·ЦЦ®јдҙ«ЛНРЕПўөД№«№ІНЁөАЈ¬ТІКЗ№өНЁОўРНјЖЛг»ъёчЦЦЖчјюөДЗЕБәЎЈ

ЈЁ1Ј©өШЦ·ЧЬПЯAB

өШЦ·ЧЬПЯABУГАҙҙ«ЛНMPU·ўіцөДөШЦ·ВлЈ¬КЗөҘПтЧЬПЯЎЈөұОўҙҰАнЖчMPU¶ФҙжҙўЖч»тНвІҝЙиұёҪшРР¶БРҙІЩЧчКұЈ¬КЧПИТӘ°СҙжҙўөҘФӘ»тНвЙиөДөШЦ·ВлЛНөҪөШЦ·ЧЬПЯЙПСЎЦРЛьЈ¬И»әуҪшРР¶БРҙЎЈөШЦ·ЧЬПЯМхКэУЙMPUРНәЕҫц¶ЁЈ¬ФЪҙуІҝ·Ц8О»»ъЦРЈ¬өШЦ·ЧЬПЯНЁіЈОӘ16МхЎЈ

ЈЁ2Ј©КэҫЭЧЬПЯDB

КэҫЭЧЬПЯDBУГАҙҙ«ЛНКэҫЭәНЦёБоВлЈ¬КЗЛ«ПтЧЬПЯЎЈНЁ№эDBЈ¬MPUҝЙҪ«КэҫЭРҙИлҙжҙўЖч»тПтНвЙиКдіцКэҫЭЈ¬ТІҝЙҙУҙжҙўЖч»тКдИлЙиұёКдИлКэҫЭЎЈКэҫЭЧЬПЯМхКэіЈәНЛщУГОўҙҰАнЖчЧЦіӨПаөИЈ¬ө«ТІУРДЪІҝОӘ16О»ФЛЛг¶шНвІҝИФОӘ8О»КэҫЭЧЬПЯөДЗйҝцЎЈ8О»»ъЦРКэҫЭЧЬПЯНЁіЈУР8МхЎЈ

ЈЁ3Ј©ҝШЦЖЧЬПЯCB

ҝШЦЖЧЬПЯCBУГАҙҙ«ЛНMPU·ўіцөДҝШЦЖРЕәЕЎўҙжҙўЖч»тНвЙиөДЧҙМ¬РЕәЕәНКұРтРЕәЕөИЎЈГҝёщҝШЦЖЧЬПЯөДРЕПўҙ«ЛН·ҪПтКЗ№М¶ЁөДЎўөҘПтөДЈ¬¶шҝШЦЖЧЬПЯЧчОӘХыМеОӘЛ«ПтөДЈ¬ИзНјЛщКҫЎЈҝШЦЖЧЬПЯөДМхКэТт»ъЖч¶шТмЈ¬ГҝМхҝШЦЖПЯЧо¶аҙ«ЛНБҪёцҝШЦЖРЕәЕЎЈ

ОўРНјЖЛг»ъІЙУГЧЬПЯҪб№№Ј¬К№өГЛьДЬ№»К®·Ц·ҪұгөШКөПЦҙжҙўЖчөДА©ідј°I/OҪУҝЪ°еөДФцјУәНјхЙЩЎЈ

ұајӯЈәadmin ЧоәуРЮёДКұјдЈә2018-05-08