您好,欢迎进入江南娱乐手机客户端 官方网站!

您好,欢迎进入江南娱乐手机客户端 官方网站!

Xilinx®Vivado®集成设计环境(IDE)通过设置对象属性的值,可以对设计对象进行物理约束。 例子包括:

•I / O约束,例如位置和I / O标准

•放置约束,例如单元格位置

•路由约束,例如固定路由

•配置约束,例如配置模式

与时序约束类似,物理约束必须保存在Xilinx设计约束(XDC)文件或Tcl脚本中,以便在打开设计时可以使用网表加载它们。 将设计加载到内存后,您可以使用Tcl控制台或使用Vivado Design Suite IDE编辑工具以交互方式输入新约束。

大多数物理约束是通过对象上的属性定义的:

set_property <property> <value> <object list>

例外是使用Pblock命令的区域约束。

严重警告

针对XDC文件中的无效约束发出严重警告,包括应用于设计中无法找到的对象的约束警告。

有关属性定义和用法,请参阅“Vivado设计套件属性参考指南”

(UG912)[参考文献11]。

网表约束

网表限制是在网表对象(如端口,引脚,网络或单元)上设置的,要求编译工具以特殊方式处理它们。

重要信息:确保您了解使用这些约束的影响。 它们可能会导致设计面积增加,设计性能降低,或两者兼而有之。

网表限制包括:

•CLOCK_DEDICATED_ROUTE

•MARK_DEBUG

•DONT_TOUCH

•LOCK_PINS

CLOCK_DEDICATED_ROUTE

在网络上设置CLOCK_DEDICATED_ROUTE以指示如何路由时钟信号。

CLOCK_DEDICATED_ROUTE属性用于时钟网络以覆盖默认路由。这是一种先进的控制,需要极其谨慎,因为它可能会影响时间可预测性和可路由性。例如,当专用时钟路由不可用时,CLOCK_DEDICATED_ROUTE可以设置为FALSE。值FALSE允许Vivado工具使用通用路由将时钟从输入端口路由到全局时钟资源,例如BUFG或MMCM资源。这仅应用作器件封装引脚分配被锁定时的最后手段,并且时钟输入不能分配给适当的时钟输入引脚(CCIO)。除非用于,否则路由将是次优和不可预测的

与FIXED_ROUTE结合。

有关此属性的更多信息,请参阅Vivado设计套件(UG949)[参考文献5]的UltraFast设计方法指南中的时钟约束。

MARK_DEBUG

在RTL中的网络上设置MARK_DEBUG以保留它并使其在网表中可见。 这允许它在编译流程中的任何位置连接到逻辑调试工具。

有关更多信息,请参阅“Vivado Design Suite用户指南:编程和调试”(UG908)[参考12]中的此链接。

DONT_TOUCH

在叶子单元格,分层单元格或网络对象上设置DONT_TOUCH以在网表优化期间保留它。 DONT_TOUCH最常用于:

•防止网络被优化掉。

带有DONT_TOUCH的网络无法通过综合或实施来吸收。 这有助于逻辑探测或调试设计中的意外优化。 要保留具有多个分层段的网络,请将DONT_TOUCH放在净PARENT(get_property PARENT $ net)上,该网络是最接近其驱动程序的网段。

•防止合并手动复制的逻辑。

有时最好手动复制逻辑,例如跨越大范围的高扇出驱动程序。 将DONT_TOUCH添加到手动复制的驱动程序(以及原始驱动程序)可防止合成和实现优化这些单元格。

注意:使用reset_property重置DONT_TOUCH属性。 将DONT_TOUCH属性设置为0不会重置该属性。

避免在分层单元上使用DONT_TOUCH来实现,因为Vivado IDE实现不会使逻辑层次结构变平。 在综合中使用KEEP_HIERARCHY来维护应用XDC约束的逻辑层次结构。

LOCK_PINS

LOCK_PINS是一个单元属性,用于指定逻辑LUT输入(I0,I1,I2,...)和LUT物理输入引脚(A6,A5,A4,...)之间的映射。

常见的用途是强制将时序关键的LUT输入映射到最快的A6和A5

物理LUT输入。

Vivado集成设计环境(IDE)支持许多与集成软件环境(ISE®)设计套件相同的I / O约束。 以下I / O属性列表并非详尽无遗

有关I / O属性的完整列表,有关I / O端口和I / O单元属性的更多信息,以及具有正确语法的编码示例,请参阅“Vivado设计套件属性参考指南”(UG912)[参考11]。

注意:除非另有说明,否则所有属性都应用于端口对象。

°有关这些属性背后的应用和方法的更多信息,

请参阅器件SelectIO文档,例如7系列FPGA SelectIO资源

用户指南(UG471)[参考13]。

重要提示:ISE Design Suite和Vivado Design Suite之间存在显着差异

在处理IOB时。 Vivado工具允许在两个端口和连接到端口的寄存器单元上设置IOB。 如果在端口及其寄存器上设置了冲突值,则以寄存器上的值为准。 Vivado工具仅使用值TRUE和FALSE。 值FORCE被解释为TRUE,并且忽略值AUTO。 与ISE不同,如果无法遵守IOB设置,Vivado工具会生成严重警告,而不是错误。

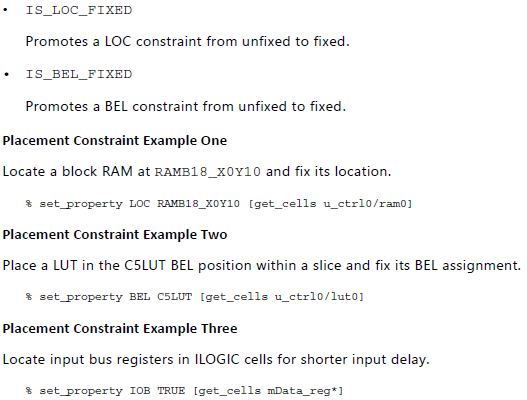

重要信息:将BEL和LOC属性分配给单元格时,必须在LOC之前分配BEL。

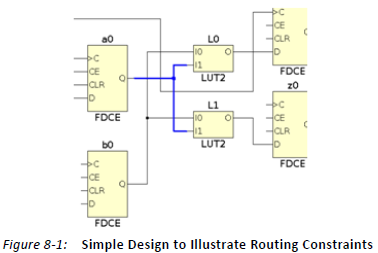

路由约束

路由约束应用于网络对象以控制其路由资源。

固定路由

固定路由是锁定路由的机制,类似于ISE中的定向路由。

锁定网络路由资源涉及三个网络属性。 见表8-1。

在内存中加载实现的设计后,您可以查询任何网络的路由信息:

路由被定义为一系列相对路由节点名称,扇出使用嵌入式花括号表示。 通过在网络上设置以下属性来修复路由:

% set_property IS_ROUTE_FIXED TRUE $net

要对XDC文件中的约束进行反向注释以供将来运行,还必须保留连接到固定网络的所有单元的放置。 您可以通过选择原理图或设备视图中的单元格来查询此信息,并查看其LOC / BEL属性

“属性”窗口中的值。 或者,您可以直接从Tcl控制台查询这些值:

% get_property LOC [get_cells {a0 L0 L1}]

SLICE_X0Y47 SLICE_X0Y47 SLICE_X0Y47

% get_property BEL [get_cells {a0 L0 L1}]

SLICEL.CFF SLICEL.A6LUT SLICEL.B6LUT

由于固定路由通常是时序关键的,因此还必须在LUT的LOCK_PINS属性中捕获LUT引脚映射,以防止路由器交换引脚。

同样,您可以从Tcl控制台查询每个逻辑引脚的站点引脚:

% get_site_pins -of [get_pins {L0/I1 L0/I0}]

SLICE_X0Y47/A4 SLICE_X0Y47/A2

% get_site_pins -of [get_pins {L1/I1 L1/I0}]

SLICE_X0Y47/B3 SLICE_X0Y47/B2

修复net netA路由所需的完整XDC约束是:

set_property BEL CFF [get_cells a0]

set_property BEL A6LUT [get_cells L0]

set_property BEL B6LUT [get_cells L1]

set_property LOC SLICE_X0Y47 [get_cells {a0 L0 L1}]

set_property LOCK_PINS {I1:A4 I0:A2} [get_cells L0]

set_property LOCK_PINS {I1:A3 I0:A2} [get_cells L1]

set_property FIXED_ROUTE { CLBLL_LL_CQ CLBLL_LOGIC_OUTS6 FAN_ALT5 FAN_BOUNCE5 {

IMUX_L17 CLBLL_LL_B3 } IMUX_L11 CLBLL_LL_A4 } [get_nets netA]

如果使用交互式Tcl命令而不是XDC,则可以使用place_cell命令一次指定多个放置约束,如下所示:

place_cell a0 SLICE_X0Y47 / CFF L0 SLICE_X0Y47 / A6LUT L1 SLICE_X0Y47 / B6LUT

有关place_cell的更多信息,请参阅Vivado Design Suite Tcl命令参考

指南(UG835)[参考文献10]。

配置约束

配置约束是应用于当前设计的比特流生成的全局约束。 这包括诸如配置模式之类的约束。

有关比特流生成属性和定义的列表,请参阅Vivado中的此链接

Design Suite用户指南:编程和调试(UG908)[参考12]。