您好,欢迎进入江南娱乐手机客户端 官方网站!

您好,欢迎进入江南娱乐手机客户端 官方网站!

Xilinx®Vivado®集成设计环境(IDE)使用Xilinx设计约束(XDC),不支持传统的用户约束文件(UCF)格式。

Xilinx设计约束(XDC)和用户约束文件(UCF)约束之间存在关键差异。 XDC约束基于标准的Synopsys设计约束(SDC)格式。 SDC已经使用和发展了20多年,使其成为描述设计约束的最流行和最成熟的格式。

XDC约束是行业标准Synopsys设计约束(SDC版本1.9)和Xilinx专有物理约束的组合。

XDC约束具有以下属性:

•它们不是简单的字符串,而是遵循Tcl语义的命令。

•它们可以像Vivado Tcl解释器一样解释为任何其他Tcl命令。

•与其他Tcl命令相同地读入和解析它们。

您可以在流程的不同点以多种方式输入XDC约束。

•将约束存储在一个或多个XDC文件中。

要在内存中加载XDC文件,请执行以下操作之一:

°使用read_xdc命令。

°将其添加到您的一个项目约束集中。 XDC文件只接受set,list和expr内置Tcl命令。有关支持的命令的完整列表,请参阅附录A,支持的XDC和SDC命令。

•使用非托管Tcl脚本生成约束。

要执行Tcl脚本,请执行以下操作之一:

°运行source命令。

°使用read_xdc -unmanaged命令。

°将Tcl脚本添加到您的一个项目约束集中。

提示:与XDC文件不同,非托管Tcl脚本可以包含用于选择设计对象和定义设计约束的任何常用Tcl命令,包括条件和循环控制结构。

重要信息:Vivado Design Suite允许您在相同的约束集中混合使用XDC文件和Tcl脚本。仅当修改的约束最初来自XDC文件而不是来自非托管Tcl脚本时,它们才会保存回原始位置。由Tcl脚本生成的约束不由Vivado Design Suite管理,无法进行交互式修改。欲获得更多信息,请参阅第2章,约束方法

重要信息:对于XDC约束,命令source和read_xdc之间的行为存在差异。 使用source命令导入的约束不会保存在检查点中与导入的顺序相同。 首先保存使用read_xdc导入的约束,然后保存使用source导入的约束。 以与应用顺序相同的顺序保存所有约束设计,使用read_xdc -unmanaged而不是source。

要在将设计加载到内存后验证特定约束的语法或影响,请使用Tcl控制台和Vivado Design Suite报告功能。 这对于分析和调试时序约束和物理约束特别有用。

约束方法论

关于约束方法论

设计约束定义了编译流程必须满足的要求,以使设计在板上起作用。并非编译流程中的所有步骤都使用所有约束。例如,物理约束仅在实现步骤期间使用(即,由布局器和路由器)。

由于Xilinx®Vivado®集成设计环境(IDE)综合和实现算法是时序驱动的,因此必须创建适当的时序约束。

过度约束或设计不足会使时序收敛变得困难。您必须使用符合您的应用程序要求的合理约束。

组织你的约束

约束方法论

关于约束方法论

设计约束定义了编译流程必须满足的要求,以使设计在板上起作用。并非编译流程中的所有步骤都使用所有约束。例如,物理约束仅在实现步骤期间使用(即,由布局器和路由器)。

由于Xilinx®Vivado®集成设计环境(IDE)综合和实现算法是时序驱动的,因此必须创建适当的时序约束。

过度约束或设计不足会使时序收敛变得困难。您必须使用符合您的应用程序要求的合理约束。

组织你的约束

Vivado IDE允许您使用一个或多个约束文件。虽然对整个编译流使用单个约束文件似乎更方便,但随着设计变得更加复杂,维护所有约束可能是一个挑战。对于使用由不同团队开发的多个IP核或大块的设计,通常就是这种情况。

导入定时和物理约束后,独立于源文件的数量或设计是否处于项目/非项目模式,可以使用write_xdc命令将所有约束导出为单个文件。写入约束

指定的输出文件的顺序与它们被读入项目或设计的顺序相同。

命令行选项write_xdc -type可用于选择要导出的约束(时间,物理或豁免)子集。

Xilinx建议您将时序约束和物理约束分开,将它们保存为两个不同的文件。 您还可以将特定于某个模块的约束保存在单独的文件中。

项目流程

您可以在创建新项目期间或稍后从Vivado IDE菜单中将Xilinx设计约束(XDC)文件添加到约束集中。

图2-1显示了项目中的两个约束集,即单XDC或多XDC。 第一个约束集包括两个XDC文件。 第二个约束集仅使用一个包含所有约束的XDC文件。

如果项目包含使用其自身约束的IP,则相应的约束文件不会出现在约束集中。 相反,它与IP源文件一起列出。

您还可以将Tcl脚本添加到约束集中作为非托管约束或非托管Tcl脚本。 Vivado Design Suite不会将修改后的约束写回非托管Tcl脚本。 Tcl脚本和XDC文件的加载顺序与Vivado IDE中显示的顺序相同(如果它们属于同一个PROCESSING_ORDER组)或命令report_compile_order -constraints报告的顺序。

如果需要,可以在多个约束集中使用XDC文件或Tcl脚本。 有关如何为项目创建和添加约束文件和约束集的更多信息,请参阅“Vivado Design Suite用户指南”中的使用约束:系统级设计

非项目流程

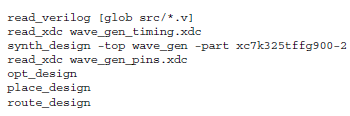

在非项目模式下,必须在执行编译命令之前单独读取每个文件。

下面的示例脚本显示了如何使用一个或多个XDC文件进行综合和实现。

语境外约束

在HD或PR流中,通常以上下文(OOC)方法合成设计的各部分。 当使用这样的流时,可以仅为OOC合成指定一些约束。 例如,在块的输入边界处传播的时钟必须

当块合成OOC时定义。 这些时钟在OOC XDC文件中定义。

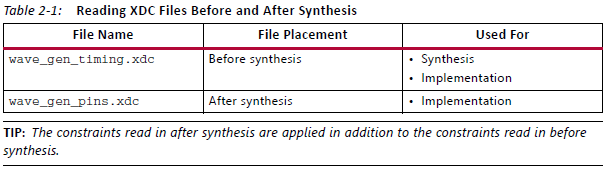

合成和实现约束文件

默认情况下,添加到约束集的所有XDC文件和Tcl脚本都用于合成和实现。 设置USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION

XDC文件或Tcl脚本上的属性可以更改此行为。 此属性可以采用TRUE或FALSE的值。

DONT_TOUCH属性不遵循USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION的属性。 如果在综合XDC中使用DONT_TOUCH属性,则无论USED_IN_IMPLEMENTATION的值如何,都会将其传播到实现。

有关DONT_TOUCH属性的更多信息,请参阅RTL属性,第58页

例如,要仅使用约束文件进行实现:

1.在“源”窗口中选择约束文件。

2.在“源文件属性”窗口中:

a 取消选中合成。

b 检查实施。

等效的Tcl命令是:

set_property USED_IN_SYNTHESIS false [get_files wave_gen_pins.xdc

set_property USED_IN_IMPLEMENTATION true [get_files wave_gen_pins.xdc

在非项目模式下运行Vivado IDE时,您可以直接在流的任何步骤之间读取约束。 在此模式下,属性USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION无关紧要。

以下编译Tcl脚本显示了如何为流的不同步骤读取两个XDC文件:

订购你的约束

由于XDC约束是按顺序应用的,并且基于明确的优先级规则进行优先级排序,因此必须仔细检查约束的顺序。 有关更多信息,请参见第7章,XDC优先级。

注意:如果多个物理约束发生冲突,则最新约束将获胜。 例如,如果I / O端口通过多个XDC文件分配了不同的位置(LOC),则为最新位置

分配给端口优先。

Vivado IDE可全面了解您的设计。 要逐步验证您的约束:

1. Run the appropriate report commands.

2. Review the messages in the Tcl Console or the Messages window.

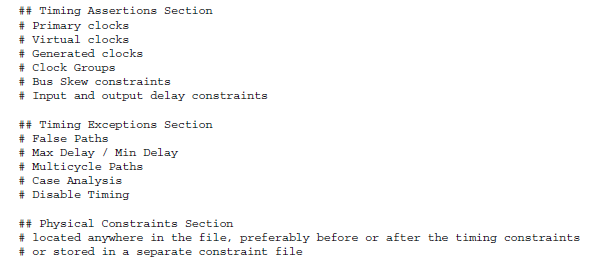

无论是为设计使用一个还是多个XDC文件,都按以下顺序组织约束。

注:应在定义生成的时钟之前定义更改时钟关系或时钟传播的案例分析约束。这包括在时钟上定义的案例分析

缓冲区导致缓冲区的输出时钟受到案例分析的影响。

从时钟定义开始。必须先创建时钟,然后才能将它们用于任何后续约束。声明之前对时钟的任何引用都会导致错误,并忽略相应的约束。这在个人中是正确的

约束文件,以及设计中的所有XDC文件(或Tcl脚本)。

约束文件的顺序很重要。您必须确保每个文件中的约束不依赖于另一个文件的约束。如果是这种情况,则必须最后读取包含约束依赖项的文件。如果两个约束文件具有相互依赖性,

您必须手动将它们合并到一个包含正确序列的文件中,或者将文件分成几个单独的文件并正确排序。

约束序列编辑

Vivado IDE约束管理器将任何已编辑的约束保存回XDC文件中的原始位置,但不会保存在Tcl脚本中。 任何新约束都保存在XDC文件的末尾

标记为目标。 在许多情况下,当您的约束集包含多个XDC文件时,其目标约束文件不是列表中的最后一个文件,并且在打开或重新加载您的设计时不会最后加载。 因此,保存在磁盘上的约束序列可能与之前在内存中的约束序列不同。

重要信息:您必须验证存储在约束文件中的最终序列是否仍按预期工作。 如果必须修改序列,则必须通过直接编辑约束文件来修改它。

这对时序约束尤为重要。

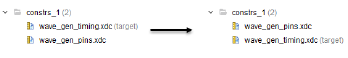

约束文件顺序

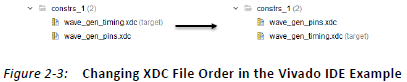

在没有任何IP的项目流中,所有约束都位于约束集中。 默认情况下,Vivado IDE中显示的XDC文件(或Tcl脚本)的顺序定义了在将精心设计或合成设计加载到工具中时工具使用的读取顺序记忆。

首先读取列表顶部的文件,最后读取底部的文件。 您只需在IDE中选择文件并将其移动到列表中的所需位置即可更改顺序。

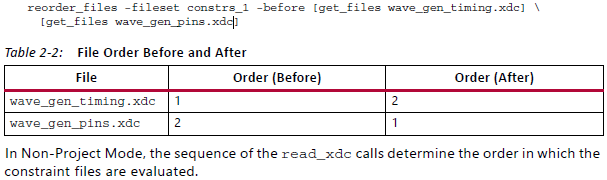

例如,在图2-3中,使用拖放操作将文件wave_gen_pin.xdc移动到文件wave_gen_timing.xdc之前。

等效的Tcl命令是:

在非项目模式下,read_xdc调用的顺序决定了约束文件的计算顺序。

约束文件使用IP核排序

许多IP内核随附一个或多个XDC文件。 在RTL项目中生成此类IP内核时,还会在各种设计编译步骤中使用其XDC文件。

例如,图2-4显示项目中的一个IP核带有一个XDC文件。

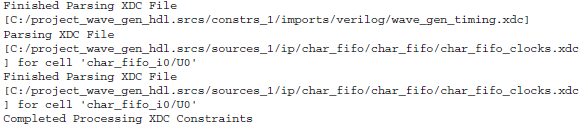

默认情况下,在用户XDC文件之前读入IP XDC文件。 以这种方式处理它允许IP创建可以在XDC中引用的时钟对象。 它还允许您覆盖由IP内核设置的物理约束,因为在IP之后评估用户约束。 对于依赖于由用户或其他IP创建的时钟对象的IP核,此顺序有一个例外(例如,get_clocks -of_objects [get_ports clka])。 在这种情况下,在用户文件之后读取IP XDC。

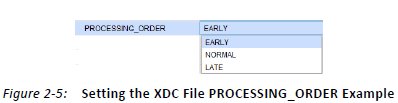

此行为由PROCESSING_ORDER属性控制,为每个XDC文件设置:

• EARLY: Files that must be read first

• NORMAL: Default

• LATE: Files that must be read last

IP XDC将其PROCESSING_ORDER属性设置为EARLY或LATE。 No IP提供属于NORMAL约束组的XDC文件。 对于属于同一个PROCESSING_ORDER组的用户XDC(或Tcl)文件,它们的相对顺序显示在

Vivado IDE确定其读取序列。 可以通过移动Vivado IDE约束集中的文件或使用reorder_files命令来修改组中的顺序。

对于属于同一PROCESSING_ORDER组的IP XDC文件,顺序由IP内核的导入或创建顺序确定。 创建项目后,无法更改此订单。

最后,用户组和IP XDC PROCESSING_ORDER组之间的相对顺序是

如下:

1. User Constraints marked as EARLY

2. IP Constraints marked as EARLY (default)

3. User Constraints marked as NORMAL

4. IP Constraints marked as LATE (contain clock dependencies)

5. User Constraints marked as LATE

注意:将其PROCESSING_ORDER设置为LATE(为了在用户约束后处理)的IP XDC文件命名为<IP_NAME> _clocks.xdc。

下图显示了如何设置PROCESSING_ORDER属性的示例:

The equivalent Tcl command is:

set_property PROCESSING_ORDER EARLY [get_files wave_gen_pins.xdc]

使用Tcl控制台中的report_compile_order -constraints命令报告由工具根据上述属性确定的XDC文件读取顺序,包括IS_ENABLED,USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION。

Changing Read Order

要在约束集中更改XDC文件或非托管Tcl脚本的读取顺序,请执行以下操作:

1.在“源”窗口中,选择要移动的XDC文件或Tcl脚本。

2.将文件拖放到约束集中的所需位置。

对于图2-3中所示的示例,等效的Tcl命令是:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] \

[get_files wave_gen_pins.xdc]

在非项目模式下,read_xdc调用的顺序决定了约束文件的计算顺序。

约束文件使用IP核排序

许多IP内核随附一个或多个XDC文件。 在RTL项目中生成此类IP内核时,还会在各种设计编译步骤中使用其XDC文件。

例如,图2-4显示项目中的一个IP核带有一个XDC文件。

更改读取顺序

要在约束集中更改XDC文件或非托管Tcl脚本的读取顺序,请执行以下操作:

1.在“源”窗口中,选择要移动的XDC文件或Tcl脚本。

2.将文件拖放到约束集中的所需位置。

对于图2-3中所示的示例,等效的Tcl命令是:

reorder_files -fileset constrs_1 -before [get_files wave_gen_timing.xdc] \

[get_files wave_gen_pins.xdc]

在非项目模式下,read_xdc或source命令的顺序确定

读取约束文件的顺序。

如果使用带有约束的IP内核,则会处理两组约束

自动如下

•不依赖于时钟的约束被分组到XDC文件中,其中PROCESSING_ORDER设置为EARLY,

•依赖于时钟的约束在XDC文件中分组

PROCESSING_ORDER设置为LATE。

默认情况下,用户XDC文件属于PROCESSING_ORDER NORMAL组。 它们在EARLY XDC文件之后和LATE XDC文件之前加载。 对于每个PROCESSING_ORDER组,IP XDC文件的加载顺序与IP核中列出的IP核的顺序相同

来源窗口。 例如,下图显示了XDC文件附带的项目IP内核之一。

打开设计时,日志文件显示最后加载了IP XDC文件:

与用户XDC文件不同,您无法直接更改IP XDC文件的读取顺序

属于同一个PROCESSING_ORDER组。 如果您必须修改订单,请执行

以下:

1.禁用相应的IP XDC文件(IS_ENABLED设置为false)。

2.复制他们的内容。

3.将内容粘贴到约束集中包含的一个XDC文件中。

4.使用完整的分层网表对象路径名更新复制的IP XDC命令

在需要的地方。 这样做是必需的,因为写入了IP XDC约束

这样一种方式,它们可以作用于IP实例。

5.查看以特殊方式处理范围约束的get_ports查询。 有关XDC范围的更多信息,请参阅约束范围,第67页。

输入约束

Vivado IDE提供了几种输入约束的方法。 除非您在文本编辑器中直接编辑XDC文件,否则必须打开设计数据库(详细说明,综合或实现)才能访问Vivado IDE中的约束窗口。

在内存中保存约束

您必须在内存中设计一个设计才能在编辑期间验证您的约束。

使用Vivado IDE用户界面编辑约束时,将发出等效的XDC命令

在Tcl控制台中,以便将其应用于内存中。必须先在内存中应用已编辑的时序约束,然后才能将其保存到XDC文件中。

在运行综合或实现之前,必须将内存中的约束保存回属于项目的XDC文件。

Vivado IDE会在必要时提出您保存约束。

执行以下操作之一以手动保存约束

注意:保存内存中的约束时,会打开一个对话框,提醒您这可能导致合成和实现过时。 选择“记住首选项”检查

此对话框上的框以禁用此警告的未来实例。

运行这些命令时,Vivado会执行以下操作:

•将所有新约束保存到约束集中标记为目标的XDC文件

与您的设计相关联。

•将所有已编辑的约束保存回源自它们的XDC文件。

注意:约束管理系统保留原始XDC文件格式

可能。

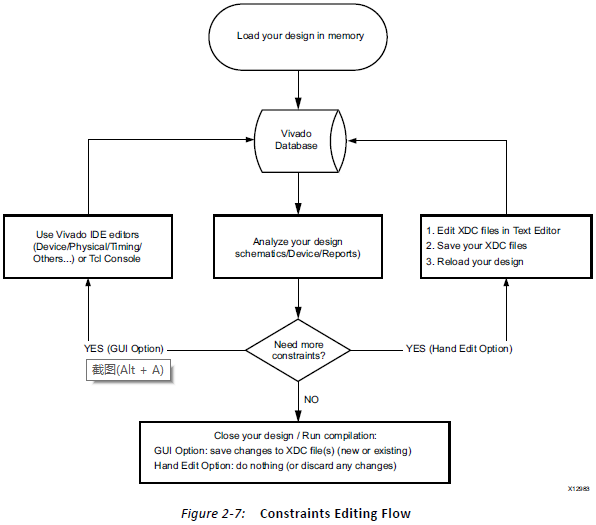

约束编辑流程选项

图2-7显示了推荐的流量选项。 不要同时使用这两个选项。 混合这些选项可能会导致您失去约束。

推荐的流程选项包括:

•用户界面选项

•手动编辑选项

用户界面选项

由于Vivado IDE管理您的约束,因此您不能同时编辑XDC文件。 当Vivado IDE保存内存内容时,会发生以下情况:

•修改的约束替换原始文件中的原始约束。

•新约束将附加到标记为目标的文件中。

•将覆盖XDC文件中的所有手动编辑。

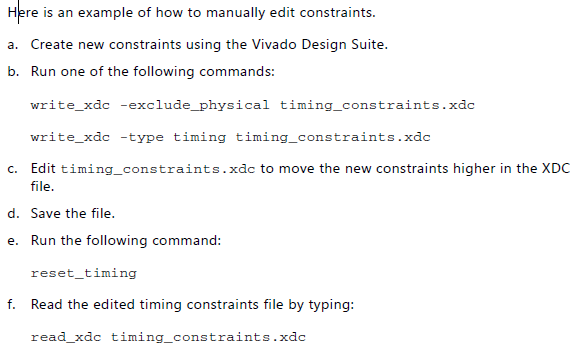

手编辑选项

使用“手动编辑”选项时,您负责编辑和维护XDC文件。 虽然您可能会使用Tcl控制台来验证某些约束的语法,

关闭或重新加载设计时,必须放弃在内存中所做的更改。

如果在保存约束时发生冲突,系统会提示您选择其中一个

以下:

Discarding the changes made in memory

• Saving the changes in a new file

• Overwriting the XDC files

约束创建是迭代的。 在某些情况下,您可以使用IDE编辑器,并在其他情况下手动编辑约束文件。

在图2-7中描述的每次迭代中,不要同时使用这两个选项。

如果在两个选项之间切换,则必须先保存约束或重新加载设计,以确保内存中的约束与XDC文件正确同步。

要在使用RTL分析时创建和编辑现有的顶级端口放置,

综合或实施意见:

1.选择I / O Planning预配置布局。

打开表2-3中显示的窗口。

有关引脚分配的更多信息,请参阅“Vivado Design Suite用户指南”中的此链接:

I / O和时钟规划(UG899)[参考3]。

布局规划

在使用RTL分析,综合或实施视图时创建和编辑Pblock:

1.选择布局规划预配置布局。

2. Open the windows shown in Table 2-4.

要在特定的BEL或SITE上创建单元格放置约束:

1.在“网表”视图中选择单元格。

2.将单元格拖放到“设备”视图中的目标位置。

有关布局规划的更多信息,请参阅“Vivado Design Suite用户指南”中的以下链接:

设计分析和关闭技术(UG906)[参考文献4]。

时序约束向导

时序约束向导识别合成或实现的设计上缺少的时序约束。 它分析网表,时钟网络连接和现有的时序约束,以便根据UltraFast设计提供建议

Vivado设计套件(UG949)[参考文献5]的方法指南。 向导的以下11页包含三类约束,后面是摘要。

包括以下步骤:

在每个步骤中,您可以接受建议的约束或通过选中或取消选中每个建议的约束来修改列表。 但是,在向导的早期取消选中建议的约束可能会阻止其他的识别

后续步骤中缺少约束。 例如,如果您决定跳过创建时钟,向导将不会识别并推荐任何引用此时钟的约束

或其自动衍生的时钟。

向导的最后一页提供了将要创建的约束的摘要。 您可以单击每个单独的超链接以查看约束详细信息,或在退出向导后在“时序约束”窗口中显示新约束。

单击“完成”后,您还可以选择生成以下建议的报告

验证设计是否完全受约束:

•创建时序摘要报告:除了check_timing报告之外,还会使用新约束报告时序松弛。 如果期限可能会显示时间违规

或者您输入的I / O延迟约束太难了。

•创建检查时间报告:此报告通过运行check_timing命令来识别缺失或不适当的约束。

•仅使用时序检查创建DRC报告:此报告运行时序DRC。

重要信息:除非单击“取消”,否则新添加的约束将自动保存到目标XDC文件中。 退出后,您可以在Timing Constraints窗口中编辑或删除新约束

如果定时约束向导引入了不安全的时序分析,则不建议使用约束。此外,该向导不会修复已存在的不适当约束

在内存中加载设计时。然而,在项目模式下使用Vivado Design Suite时,创建所有丢失的时钟后,某些无效约束可能会生效;

有关更多详细信息,请参阅下面的约束处理顺序和无效约束。此外,在使用向导之后,如果check_timing或report_drc仍标记一些约束问题,则通常是由于源XDC文件中已存在的约束问题。直接解决这些问题,而不是使用向导来解决它们。

约束处理顺序和无效约束

时序约束向导建议缺少定义时钟或引用时钟的约束,这些约束将在项目模式下保存在目标XDC文件的末尾,或者在其他模式的所有约束结束时保存。出于这个原因,你必须明白

以下规则:

•项目模式:在启动“计时约束”向导之前,必须指定目标XDC文件,其处理顺序设置为“正常”。目标XDC文件必须属于在内存中打开且当前选定的设计的约束集。目标XDC文件在其他XDC文件中的位置很重要,因为它指定了

建议的约束将在何时应用并保存。此外,向导会尝试重新应用属于目标XDC文件之后解析的XDC文件的任何无效约束,以便提供最完整和准确的建议。

例如,考虑来自synth_1的网表在内存中使用约束集constr_1运行。此约束集包含序列中的三个XDC文件

a.xdc,b.xdc和c.xdc。如果选择b.xdc作为目标XDC文件,并且每个文件包含无效约束,则“时序约束”向导将应用建议的时钟,然后从c.xdc重新应用无效约束,然后继续下一步并发现其他缺少的约束。

非项目或设计检查点(DCP)模式:您无法在这些模式下指定目标XDC文件,因此“时序约束”向导会在约束序列的最后位置推荐并应用新约束。 这相当于在Tcl控制台中输入新约束或通过Timing Constraints窗口输入新约束。 在这些模式下,向导不会尝试重新应用无效约束。 如果需要在整个约束序列中更早地应用新约束以解决约束依赖性或优先级问题,则必须编辑约束

手动顺序。

您可以使用Timing Constraints窗口查看更新的时序约束序列。 查看新约束后,可以将序列保存到DCP中。

向导打开时可用的报告功能

当Timing Constraints向导打开时,它会阻止Vivado IDE中的大多数操作,包括使用Tcl控制台或运行时序分析,以避免数据库差异。 向导窗口始终位于其他Vivado IDE窗口的前面。 如果你

需要访问Vivado IDE菜单或窗口,您必须将向导窗口移到一边。

Timing Constraints向导打开时,只有以下功能可用:

• Reporting and visualizing the clock networks

向导的大多数页面都有按钮来生成和访问时钟网络报告,以便可视化时钟拓扑,它们的源点以及某些时钟的共享段。

请参阅Vivado Design Suite用户指南:设计分析和关闭技术

(UG906)[参考4]了解有关时钟网络报告的更多详细信息。

•在源文件中搜索名称或在内存中搜索设计中的对象

“编辑”菜单中提供了“查找和查找文件”对话框。您可以使用这些对话框用于在输入时检索有关设计的一些信息

向导中的约束。

•创建和查看原理图

您可以在主Vivado IDE窗口中选择设计对象并将其可视化原理图。所有原理图功能均可用。只有时间的最后一步

约束向导,异步时钟域交叉,支持方便在“时序路径”选项卡中选择一个或多个条目时的原理图交叉探测。

请参阅Vivado Design Suite用户指南:使用Vivado IDE(UG893)[参考7]

有关使用原理图的更多信息。

•使用Timing Constraints窗口可视化内存中的约束

向导的每个页面都包含一个选项卡,显示相同的现有约束键入步骤建议的类型。这样便于快速查看详细信息

已在XDC文件中创建的约束。有关所有时序约束的完整视图

在内存中,Timing Constraints窗口显示完整的约束序列,由XDC文件组织,包括范围信息。它还显示无效限制。

约束在向导中编辑

向导的每个步骤都可以推荐几个约束。 根据约束,

您必须采取以下操作之一:

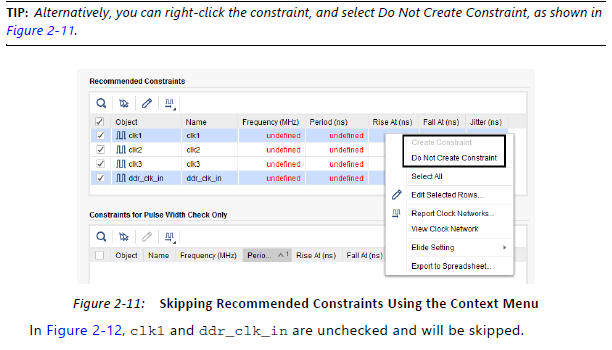

•使用以下方法之一取消选中您不想创建的约束

方法:

°通过取消选中每一行,从列表中删除每个约束,一次一个。

°通过取消选中表格的左上角复选框来删除所有约束。

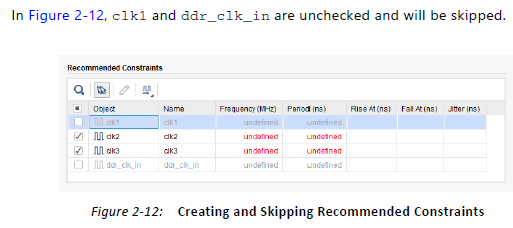

通过单击显示未定义的单元格输入缺少的值(例如,图2-12中的clk2和clk3的频率或周期值)。

您可以通过选择相应的行并单击Edit Selected Rows按钮同时编辑多个约束,如图2-13所示。

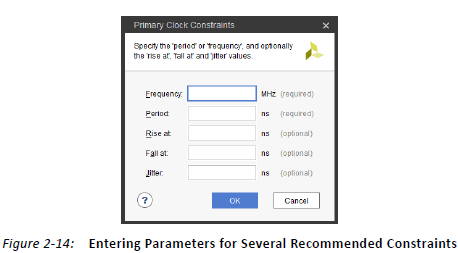

Next, fill out any required fields, such as Frequency and Period as shown in Figure 2-14.

限制。

•如果不需要采取任何措施,只需查看约束。

检查并完成所有已检查的建议约束后,单击

单击下一步继续下一页。 您错过的任何条目都会阻止向导进入下一步。

您可以使用“后退”按钮重新访问页面。 如果在上一页上编辑任何约束并单击“下一步”,则向导将重新分析设计并推荐新约束

因此。 在大多数情况下,将恢复先前建议的不受更改影响的约束。 如果您只查看上一页而不修改任何页面

建议约束,向导不会重新运行任何分析,这通常可以节省运行时间。

重要信息:您无法使用“时序约束”向导编辑现有时序约束。 代替,

您必须使用Timing Constraints窗口。

向导推荐的约束

主时钟

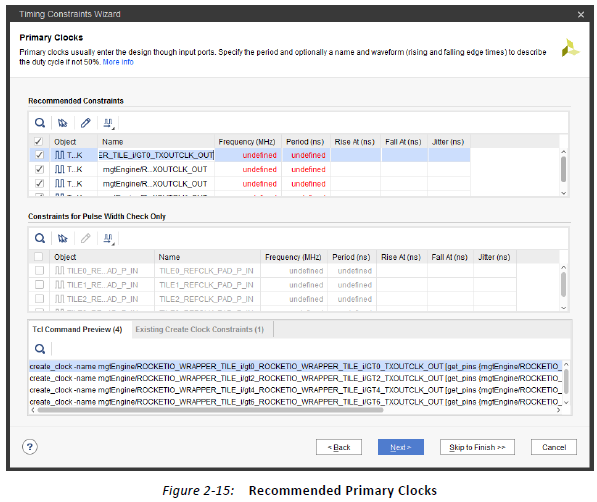

向导标识两类时钟,如图2-15所示。

•计算时序松弛所需的主时钟

建议约束表中显示建立/保持/恢复/删除检查。

•仅执行脉冲宽度检查所需的时钟(min_period,

max_period,max_skew,min_low_pulse_width和min_high_pulse_width)

出现在“仅限脉冲宽度检查限制”表中。 默认情况下,这些时钟

未选中,因为它们仅用于报告目的而不会影响

实施工具的结果质量。

向导会自动识别约束的正确时钟源点。 它

对应于时钟信号在物理上进入设计的时钟树根。 在

大多数情况下,时钟源点是输入时钟端口,在某些特殊情况下它是

X-Ref目标 - 图2-15

•计算时序松弛所需的主时钟

建议约束表中显示建立/保持/恢复/删除检查。

•仅执行脉冲宽度检查所需的时钟(min_period,max_period,max_skew,min_low_pulse_width和min_high_pulse_width)

出现在“仅限脉冲宽度检查限制”表中。 默认情况下,这些时钟未经检查,因为它们仅用于报告目的,不会影响实现工具的结果质量。

向导会自动识别约束的正确时钟源点。 它对应于时钟树根,其中时钟信号实际进入设计。 在大多数情况下,时钟源点是输入时钟端口,在某些特殊情况下,它是没有定时弧的基元的输出。 例如,在7系列设备中,向导会识别GT_CHANNEL基元输出上缺少的主时钟。 对于UltraScale™器件,Vivado设计套件能够根据输入时钟特性和GT_CHANNEL自动导出GT_CHANNEL输出时钟

配置和连接。 因此,向导会建议位于设计边界上GT_CHANNEL单元上游的主时钟。

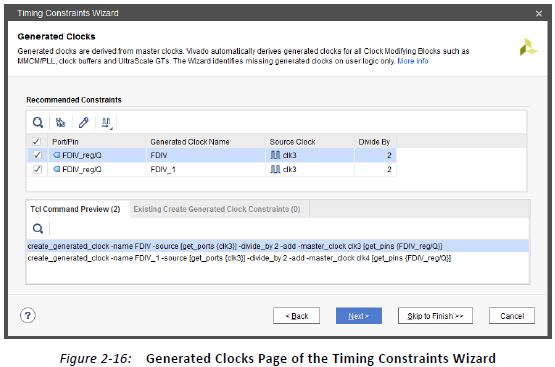

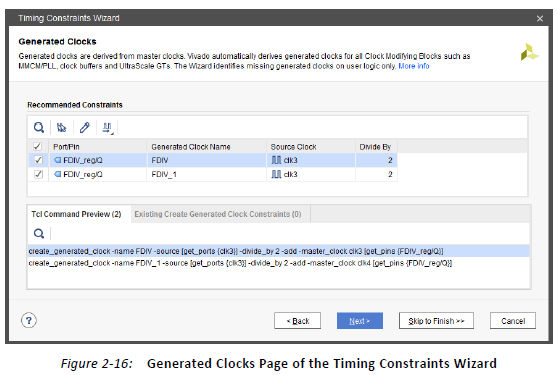

生成的时钟

时序约束向导建议在顺序单元的输出上创建生成时钟,直接驱动其他顺序单元的时钟引脚或

通过一些互连逻辑。 与PLL或MMCM不同,用户逻辑不能乘以主时钟的频率,因此向导仅提供指定除法系数的选项,如图2-16所示。

当多个主时钟到达生成的时钟源点时,向导将使用唯一的名称和对个人的明确引用创建所有相应的生成时钟

主时钟。 图2-16说明了两个时钟(clk3和clk4)到达顺序单元FDIV_Reg的情况。 因此,建议使用两个生成的时钟约束(FDIV和FDIV_1)。

注意:某些时钟拓扑(例如时钟路径上的级联寄存器)可能需要多次运行“时序约束”向导才能发现所有丢失的生成时钟。

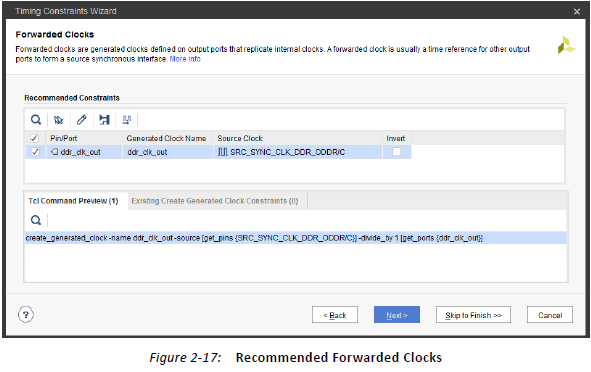

转发时钟

Timing Constraints向导建议在输出端口上生成时钟约束,该输出端口由具有常量输入的双倍数据速率寄存器驱动。 基于输入恒定连接性,将生成的时钟相位调整为正(0度相移)或反相(180度相移)。 约束中使用的主时钟是

到达双倍数据速率寄存器的时钟引脚的时钟。 请参见图2-17中“推荐约束”表的“源时钟”列。

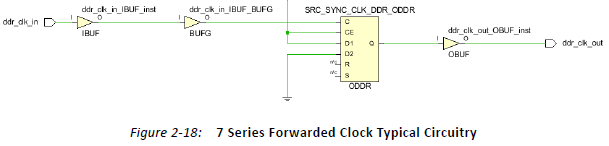

对于7系列器件系列,向导识别的拓扑结构如下所示

图2-18。 主时钟或输出缓冲器的性质没有限制。

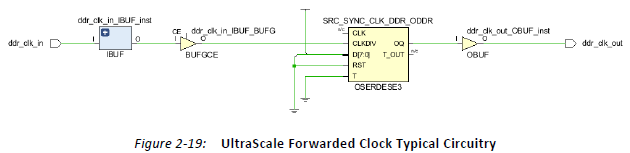

对于UltraScale器件系列,ODDR和ODDRE1原语会自动重定向到OSERDESE3,其属性为ODDR_MODE = TRUE。 向导识别图2-19中所示的拓扑,其中OSERDESE3 / D [0]连接到1和

OSERDESE3 / D [4]连接到0(无相移)

外部反馈延迟

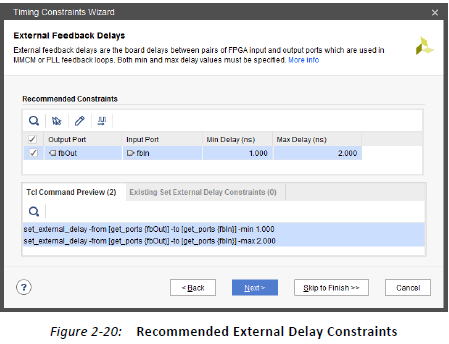

Timing Constraints(时序约束)向导分析设计中存在的MMCM和PLL单元的反馈环路连接。 建议使用外部延迟约束(最小和最大)

当CLKFBIN和CLKFBOUT引脚通过IO缓冲器和MMCM或PLL属性COMPENSATION = EXTERNAL连接到设计端口时。 图2-20说明

建议的外部延迟约束。

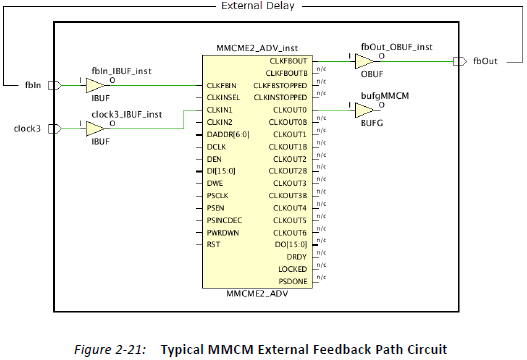

图2-21显示了具有外部反馈路径电路的典型MMCM。

在当前的Vivado Design Suite版本中,当反馈路径中有连续单元时,Timing Constraints向导不能建议外部延迟约束,

例如ODDR,用于生成转发时钟。 在这种情况下,您必须在退出向导后手动或使用Timing Constraints窗口创建外部延迟约束。

输入延迟

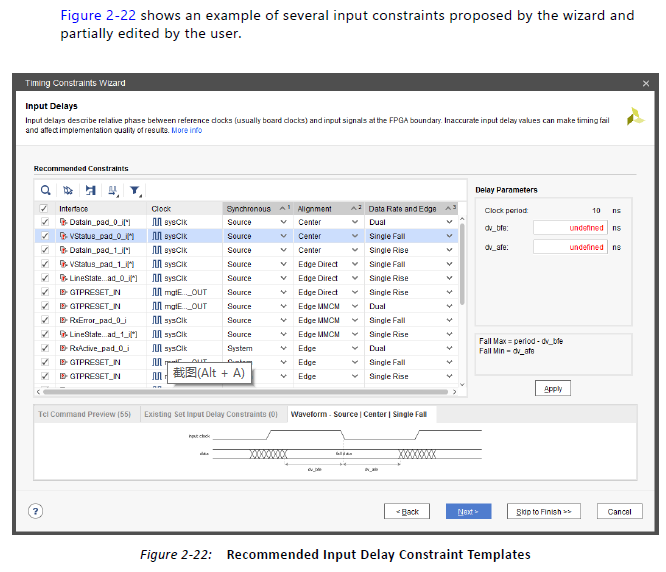

Timing Constraints(时序约束)向导分析来自输入端口的所有路径,以识别设计中的目标时钟及其活动边缘。 根据此信息,向导会建议基于的基本系统同步输入延迟约束

Vivado IDE中提供的XDC模板(有关模板,请参阅XDC模板,第55页)。 与所选模板关联的波形显示在窗口底部

在“推荐约束”表中选择约束条目时,在“波形”选项卡中。

对于每个约束,您可以编辑三个特征,以指定与电路板上实际接口时序对应的相应波形:

•同步描述时钟数据关系的性质。

°系统(用于系统同步接口):当数据通过1个周期或相隔1/2周期的不同时钟边沿启动和捕获时使用此设置。

°Source(用于源同步接口):当数据以相同的时钟边沿启动和捕获时使用此设置。

•对齐描述了与活动时钟相关的数据转换对齐。

°仅适用于系统同步接口:

- Edge:当时钟和数据同时转换时使用此设置。