您好,欢迎进入江南娱乐手机客户端 官方网站!

您好,欢迎进入江南娱乐手机客户端 官方网站!

一些设计者可互换地使用术语属性和约束。 其他设计师给他们不同的意义。 此外,使用某些语言结构的术语相似但是意义不同

Xilinx®使用术语属性和约束如下定义。

属性

属性是与设备体系结构原语组件相关联的属性,其通常影响实例化的组件功能或实现。

属性通过以下方式传递:

•通用地图(VHDL)

•实例化基元组件时传递的Defparams或内联参数(Verilog的)

所有属性都在Xilinx库指南中作为原始组件描述的一部分进行了描述。

CPLD Fitter

The following constraints apply to CPLD devices:

BUFG (CPLD)

Collapse (COLLAPSE)

CoolCLOCK (COOL_CLK)

Data Gate (DATA_GATE)

Fast (FAST)

Input Registers (INREG)

Input Output Standard (IOSTANDARD)

Keep (KEEP)

Keeper (KEEPER)

Location (LOC)

Maximum Product Terms (MAXPT)

No Reduce (NOREDUCE)

Offset In (OFFSET IN)

Offset Out (OFFSET OUT)

Open Drain (OPEN_DRAIN)

Period (PERIOD)

Prohibit (PROHIBIT)

Pullup (PULLUP)

Power Mode (PWR_MODE)

Registers (REG)

Schmitt Trigger (SCHMITT_TRIGGER)

Slow (SLOW)

Timing Group (TIMEGRP)

Timing Specifications (TIMESPEC)

Timing Name (TNM)

Timing Specification Identifier (TSidentifier)

VREF

Wire And (WIREAND)

逻辑约束

逻辑约束是在映射或拟合之前附加到元素的约束。

•逻辑约束有助于使设计性能适应预期的最坏情况。

•当您执行以下操作时,逻辑约束将转换为物理约束:

1.选择特定的Xilinx®架构,以及

2.放置和布线,或适合设计。

•您可以使用输入设计中的属性附加逻辑约束,这些属性将写入网表约束文件(NCF)或NGC网表或用户

约束文件(UCF)。

•三类逻辑约束是:

- 放置限制

- 相对位置约束

对于FPGA器件,相对位置约束:

¨将逻辑元素分组为离散集。

¨允许您定义集合中任何元素相对于的位置

集合中的其他元素,无论最终放置在整体设计中。

- 时间限制

时序约束允许您指定允许的最大延迟或倾斜

在任何给定的路径或网络上。

物理约束

注意本节仅适用于FPGA器件。

物理约束是附加到物理设计中的元素的约束。

映射(mapping)

•物理设计是映射后的设计。

•映射设计时,(1)网表和(2)用户约束文件(UCF)中的逻辑约束将转换为适用于特定的物理约束

建筑。

•物理约束在映射期间创建的物理约束文件(PCF)中定义。

物理约束文件(PCF)

物理约束文件(PCF):

•是映射器生成的文件。

•包含两个部分:

- 原理图

包含基于网表和UCF中的逻辑约束的物理约束。

- 用户

¨可用于添加任何物理约束。

¨Xilinx®建议您将用户生成的约束放在UCF中,而不是放在NCF或PCF中。

Mapping Directives

Mapping directives instruct the mapper to perform specific operations.

Mapping Directives(Mapping指令指示映射器执行特定操作。制图指令)

• Area Group

• BEL

• Block Name

• DCI Value

• Drive

• Fast

• Hierarchical Block Name

• Hierarchical Lookup Table Name

• HU Set

• IOB

• Input Output Block Delay

• Input Output Standard

• Keep

• Keeper

• Lookup Table Name

• Map

• No Delay

• Pulldown

• Pullup

• Relative Location

• Relative Location Origin

• Relative Location Range

• Save Net Flag

• Slew

• U Set

• Use Relative Location

• XBLKNM

放置限制(Placement Constraints)

本节描述FPGA设计中每种逻辑元件的放置约束,包括:

• Flip-Flop

• 只读存储器

• 内存

•BUFT

•CLB

•IOB

•I / O.

•边缘解码器(Edge decoder)

•全局缓冲区(Global buffer)

各个逻辑门,如AND或OR门:

•在读取约束之前映射到CLB函数生成器。

•不能约束。

指定约束

大多数约束可以在:

•HDL源代码,或

•用户约束文件(UCF)

在约束文件中,每个放置约束作用于一个或多个符号。 设计中的每个符号都带有唯一的名称,该名称在输入文件中定义。 在约束语句中使用此名称来标识符号。

区分大小写

•UCF和NCF区分大小写。

•标识符名称(对象名称,例如网络名称)必须与案例完全匹配

源设计网表中存在的名称。

•Xilinx®关键字(例如LOC,PROHIBIT,RLOC和BLKNM)可以全部大写或全部小写输入。 不允许混合案例。

网表映射和放置约束

以下约束控制网表中符号的映射和放置:

•BLKNM

•HBLKNM

•HLUTNM

•LOC

•LUTNM

•禁止

•RLOC

•RLOC_ORIGIN

•RLOC_RANGE

•XBLKNM

相对位置(RLOC)约束

RLOC约束将逻辑元素分组为离散集。

•您可以定义集合中任何元素相对于其他元素的位置

在集合中,无论最终放置在整体设计中。

•例如,如果RLOC约束应用于按列组织的一组八个触发器,则映射器将保持列顺序并将整组触发器作为单个单元移动。

•相比之下,绝对LOC约束将设计元素限制在FPGA裸片上的特定位置,与其他设计元素无关。

Placement Constraints

• AREA_GROUP

• BEL

• LOC

• LOCATE

• Prohibit

• RLOC

• RLOC_ORIGIN

• RLOC_RANGE

• USE_RLOC

路由指令

路由指令指示PAR执行特定操作。

•AREA_GROUP

•CONFIG_MODE

•LOCK_PINS

综合约束

综合约束指导特定设计或硬件描述语言(HDL)代码的综合工具优化技术。 约束要么嵌入在源代码中,要么包含在单独的综合约束文件中。

以下约束是综合约束:

• 从到

•IOB

• 保持

•MAP

•MARK_DEBUG

•OFFSET IN

•OFFSET OUT

•期间

•TIG

•TNM

•TNM_NET

综合约束文档

XST综合约束记录在:

•适用于Virtex-4,Virtex-5,Spartan-3和更新CPLD器件的XST用户指南(UG627)

•适用于Virtex-6,Spartan-6和7系列器件的XST用户指南(UG687)

软件供应商的文档中记录了其他综合约束。

时间限制

Xilinx®软件使您能够使用全局或路径特定的时序约束来指定精确的时序要求。

定时讨论了定义约束的推荐方法

关闭用户指南(UG612)。

以下是时序约束和相关的分组约束:

• Asynchronous Register

• Disable

• Enable

• From Thru To

• From To

• Maximum Skew

• Offset In

• Offset Out

• Period

• Priority

• System Jitter

• Temperature

• Timing Ignore

• Timing Group

• Timing Specifications

• Timing Name

• Timing Name Net

• Timing Point Synchronization

• Timing Thru Points

• Timing Specification Identifier

• Voltage

Configuration Constraints

• Configuration Mode

• DCI Cascade

• MCB Performance

• Stepping

• Post CRC

• Post CRC Action

• Post CRC Frequency

• Post CRC INIT Flag

• VCCAUX

• VREF

• Internal Vref Bank

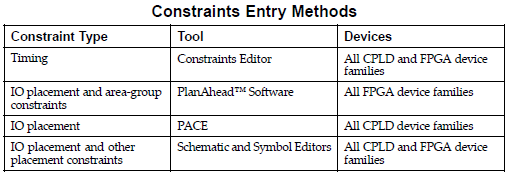

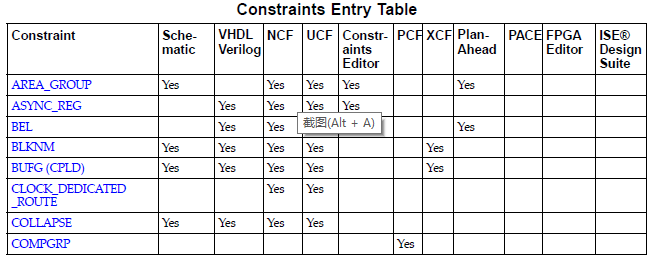

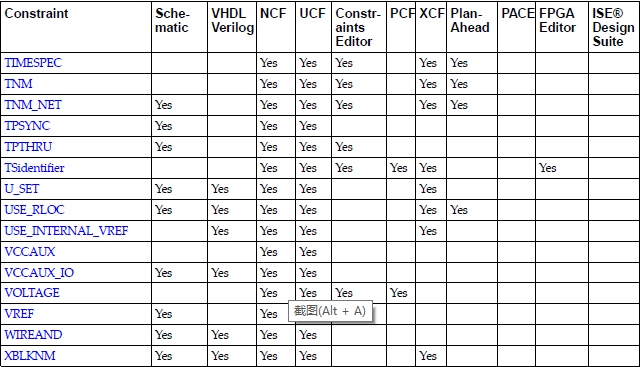

Xilinx约束的进入策略

下表显示了ISE®DesignSuite用于输入给定约束类型的功能。

下表显示了ISE®DesignSuite用于输入给定约束类型的功能。

原理图设计

遵循以下规则,将Xilinx®约束作为符号或示意图中的属性添加:

•如果约束适用于网络,请将其作为属性添加到网络中。

•如果约束适用于实例,请将其作为属性添加到实例。

•您无法添加PART和Prohibit等全局约束。

•您不能添加附加到时序规范或时序组的任何时序规范。

•以全部大写或全部小写形式输入属性名称和值。 不允许混合大写和小写。

有关创建,修改和显示属性的更多信息,请参阅“原理图和符号编辑器帮助”。

可以在原理图中输入的任何约束的语法在该约束的部分中描述。 有关正确的原理图语法的示例,请参阅BEL中的原理图语法示例。

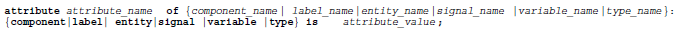

VHDL属性

在VHDL代码中,可以使用VHDL属性指定约束。 在使用它之前,必须使用以下语法声明约束:

attribute attribute_name:string;

例

属性RLOC:string;

可以在实体或体系结构中声明属性。

•如果在实体中声明属性,则它在实体和体系结构主体中都可见。

•如果在体系结构中声明属性,则不能在实体声明中使用它。

声明属性后,您可以指定VHDL属性,如下所示:

接受的attribute_values取决于属性类型。

例一

属性RLOC:string;

u123的属性RLOC:label是“R11C1.S0”;

示例二属性bufg:string;

my_clock的属性bufg:signal是“clk”;

对于Xilinx®,最常见的对象是信号,实体和标签。 标签描述组件的实例。

注意必须在输出端口上使用signal属性。

VHDL不区分大小写。

在某些情况下,现有的Xilinx约束不能用于属性,因为它们也是VHDL关键字。 要避免此命名冲突,请使用约束别名。 每个Xilinx约束都有自己的别名。 别名是预先设置的原始约束名称

前缀XIL_例如,RANGE约束不能直接在属性中使用。 请改用XIL_RANGE。

Verilog属性

Verilog属性以星号(*)为界,并使用以下语法:

(* attribute_name = attribute_value *)

哪里

•attribute在其引用的信号,模块或实例声明之前。

•attribute_value是一个字符串。 不允许使用整数或标量值。

•attribute_value介于引号之间。

•默认值为1.(* attribute_name *)与(* attribute_name =“1”*)相同。

Verilog属性语法示例一

(* clock_buffer =“IBUFG”*)输入CLK;

Verilog属性语法示例二

(* INIT =“0000”*)reg [3:0] d_out;

Verilog属性语法示例三

总是@(current_state或重置)

begin(* parallel_case *)(* full_case *)

case(current_state)

Verilog属性语法示例四

(* mult_style =“pipe_lut”*)MULT my_mult(a,b,c);

Verilog限制

不支持Verilog属性:

•信号声明

•声明

•端口连接

•表达式运算符

Verilog Meta评论

也可以使用元注释在Verilog代码中指定约束。 Verilog

format是首选语法,但仍支持元注释样式。 使用

语法如下:

//合成属性AttributeName [of] ObjectName [是] AttributeValue

Verilog Meta评论示例

// u123的合成属性RLOC是R11C1.S0

//合成属性HU_SET u1 MY_SET

// my_clock的合成属性bufg是“clk”

约束