您好,欢迎进入江南娱乐手机客户端 官方网站!

您好,欢迎进入江南娱乐手机客户端 官方网站!

串行外围总线 (SPI)

N76E003系列提供支持高速串行通信的SPI模块。SPI 为微控制与外设 EEPROM, LCD 驱动, D/A 转换之间提供

全双工、高速、同步传输的总线。可提供主机从机模式传输,速度可达到时钟频率FSYS/2,支持传输完成标志位

和“写”冲突标志位。在多主机系统中,SPI 支持主机模式错误用以防止主机冲突。

图14-1展示了SPI的简单体系结构。SPI的主要模块有SPI控制寄存器,SPI状态逻辑,波特率控制和管脚逻辑控

制。为了传送数据和接收数据,SPI 提供了移位寄存器和读数据缓冲器。因为无论传送数据或是接收数据都是双

缓存,所以传输端时,在前一个数据发送完成前,也可以写入下一笔把数据。接收端能读取读数据缓存,在移位寄

存器接收第二个数据时,同时前一个接收的数据将被传送到读数据缓存。

SPI 接口有四个管脚,分别是主进/从出(MISO),主出/从进(MOSI),移位时钟(SPCLK), 和从机选择( SS )。

MOSI脚用于传输主机到从机的8位数据,所以MOSI是一个主机设备的输出引脚,从机设备的输入引脚。相应

的,MISO用于接收从机到主机的串行数据。

SPCLK引脚为主机模式下的时钟输出,从机的输入时钟。移位时钟用于MOSI和MISO脚之间数据传输的同步时

钟。主机模式发送8个移位时钟周期,在总线上交换一个字节数据。位移时钟由主机输出,所以一组SPI传输系

统上只能有一个主机以避免设备冲突。

从机设备通过设定从机选择脚 ( SS )选择。当需要访问任何从机时,该从机的此信号脚必须保持低。当SS 为

高,该从机访问将被禁止。若为多从机模式,在同一时刻必须保持只有一个从机被选定。对于主机, SS 脚不做

任何用途,可配置为普通端口另做他用。SS可用于多主机模式下主机模式错误侦测功能

N76E003也提供自动激活片选脚功能,通过自动触发SS来传输字节。

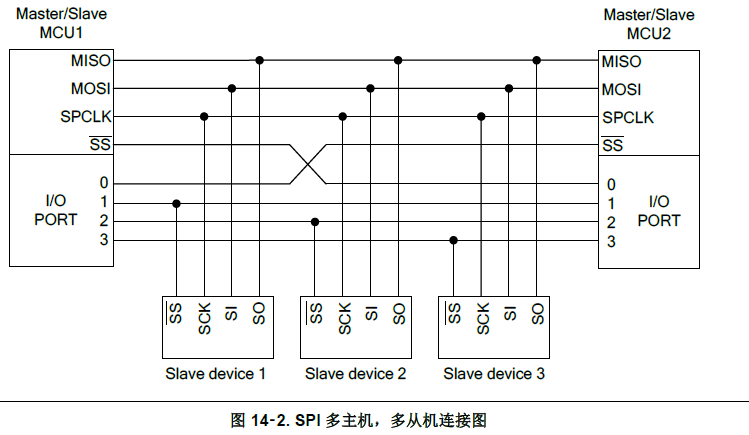

图 14?2为典型的SPI设备连接图。通信总线通过3根信号线相连, MOSI ~ MOSI, MISO ~ MISO, 和 SPCLK ~

SPCLK。主机通过一个并口的4个管脚来控制4个 ? 脚,从而实现每个 ? 线分别控制每个从机。MCU1 和 MCU2

可以任意定义为主机或从机模式。SS需配置为主机模式侦测功能避免多主机冲突。

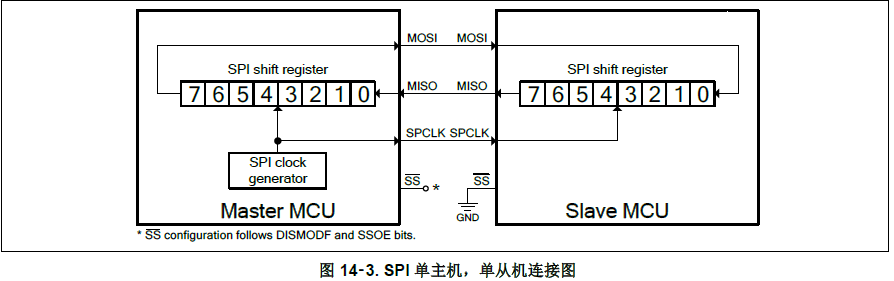

图 14?3表示SPI 模块单主机/从机互连简图。在传输时,主机通过MOSI线向从机发送数据。同时,主机也通过MISO线由从机接收数据。此时主机和从机的两个移位寄存器可被视为一个16位的循环移位寄存器。因此,当主机向从机发送数据时,从机数据也同时推向主机。这样通过两mcu的SPI移位寄存器,就完成了交换数据。

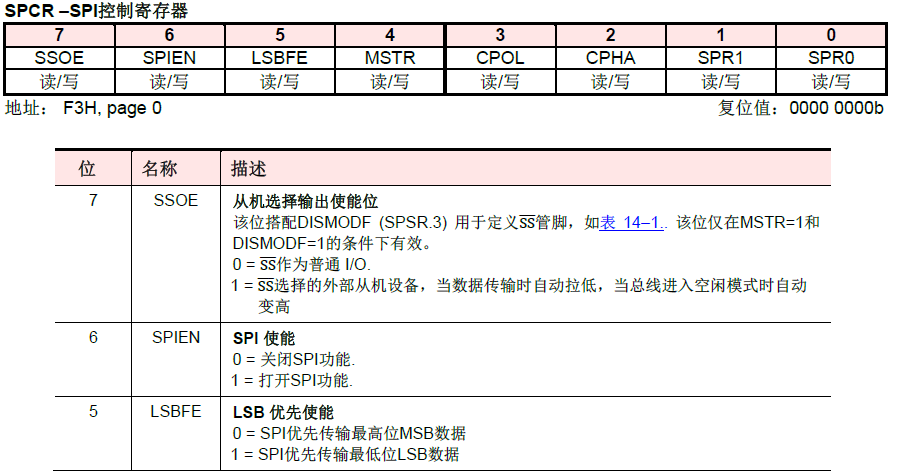

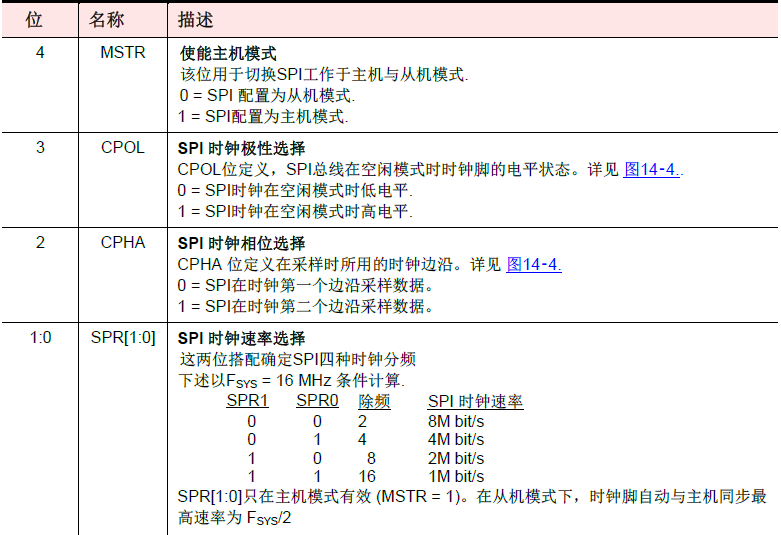

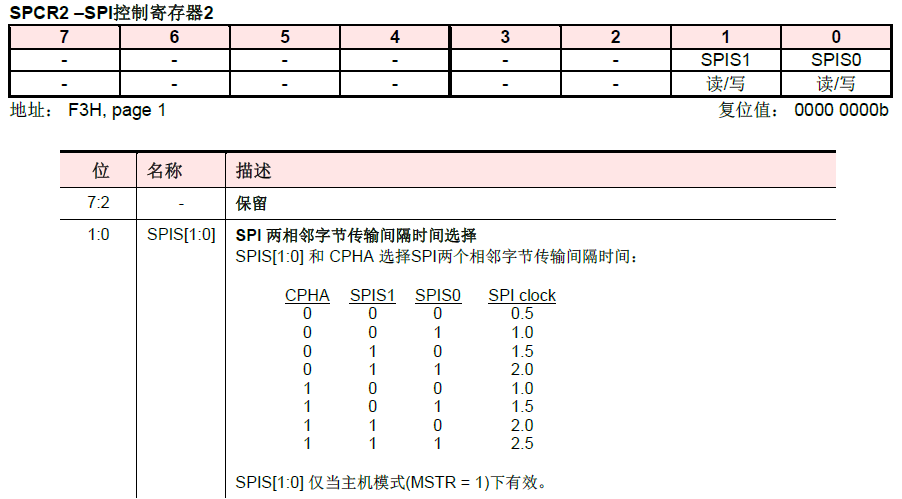

默认情况下,SPI先发送MSB 。当LSBFE (SPCR.5) 置1,SPI首先发送LSB,该位不会影响寄存器内MSB/LSB的排列顺序。注,下述全部是基于 LSBFE为0的情况,MSB 首先被发送和接收。控制寄存器 (SPCR), SPI 状态寄存器 (SPSR), SPI 数据寄存器 (SPDR) 这三个寄存器用于SPI传输。这些寄存器提供控制,状态检测,数据存储以及时钟发生设置。下面描述SPI寄存器的相关功能。

主机模式

主机模式

MSTR (SPCR.4)位置1,SPI工作在主机模式。整个SPI系统中只允许一个主机启动传输。每次传输总是由主机发起,对主机SPDR寄存器的写开始传送。在SPCLK控制下在MOSI管脚传送数据。同时,MISO管脚接收数据。在8位数据传输完毕后,SPIF (SPSR.7)由硬件自动置位以示完成一个字节数据传输。同时接收到的数据也会传送到SPDR。用户可以从SPDR读出数据,并清除SPIF。14.2.2 从机模式

设定MSTR为0,SPI将工作在从机模式。当作为从机模式时,SPCLK管脚变为输入脚,它将作为时钟输入被另外一个主机SPI设备的输出时钟控制, SS管脚也变为输入脚。当从机设备的SS 管脚不为低时,主机设备不能与从机交换数据。在数据传输开始前和数据传输完成前,SS 管脚都需要保持低电平状态。如果SS 变为高电平,SPI将被迫进入闲置状态。如果SS 管脚在传输的过程被置高,那么传输将被取消,接收移位缓存区里剩下的位数将变高,同时也将进入闲置状态。

在从机模式下,数据通过MOSI管脚从主机向从机传输,通过MISO管脚从从机向主机传输。通过主机SPCLK的时钟控制,数据进入位移寄存器。在移位寄存器接收到一个字节后,数据将移到读数据缓存,同时SPIF置1。对SPDR的读操作实际上就是对读缓冲器的一次读操作。为了防止缓冲器溢出或因溢出导致数据丢失,从设备必须在数据第二次从移位寄存器向读缓冲器传送前,把数据从SPDR读出和把SPIF清零。

时钟格式和数据传输

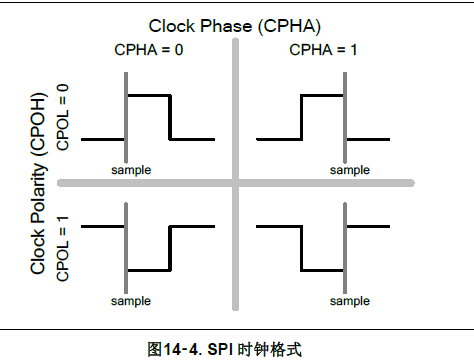

为了适应各种各样的同步串行外设,SPI提供时钟极性位CPOL(SPCR.3)和时钟相位位CPHA(SPCR.2)寄存器用以控制。如图14?4.所示,CPOL和CPHA组合出四种不同的时钟格式。 CPOL 位表示空闲状态时SPCLK脚电平。 CPHA位定义表示是MOSI和MISO上时钟的哪个边沿用来采样。在同一系统上的主从设备中,CPOL和CPHA的配置应该是相同的。传输不同的数据格式,将产生随机错误结果。

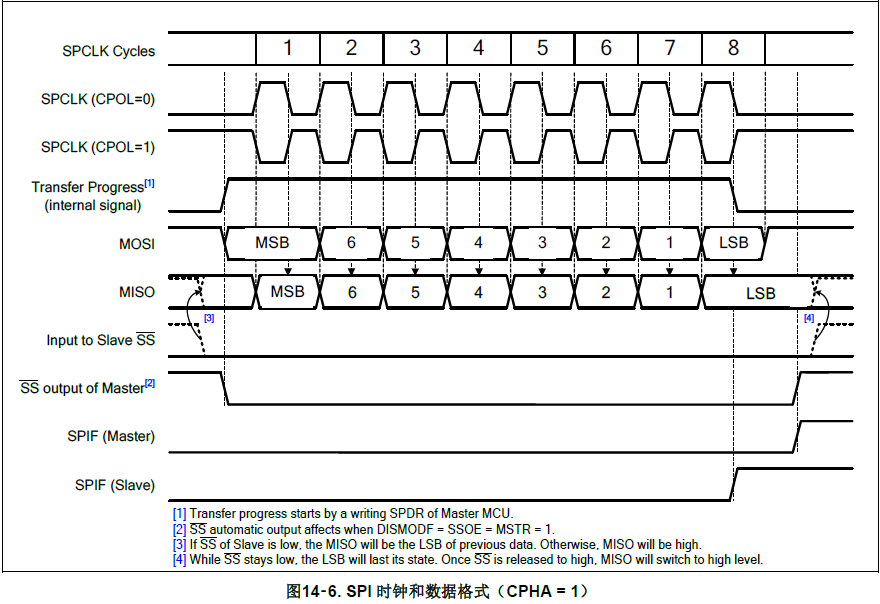

在SPI传输中,总是由主机启动传输。如果SPI被选定作为主模机式(MSTR = 1)并且打开传输(SPIEN=1),对主机的SPI数据寄存器(SPDR)写入数据将启动SPI时钟和数据传输。传出一个字节的同时会接收一个字节的内容,此后SPI时钟停止,主机和从机的SPIF(SPSR.7)同时被置1 。如果SPI中断使能位ESPI(EIE.0)设置为1,全局中断使能(EA= 1),将执行SPI的(ISR)中断服务程序。

关于从机模式下, SS 信号需要注意。如图14?4.所示,CPHA=0时, SPCLK第一个边沿为MSB的采样点(LSBFE= 0,MSB优先发送为例)。因此,从机必须在SPCLK第一个采样边沿出现之前先把MSB传出。SS 的下降沿可用于准备MISO的MSB。因此,每次成功串行传输一个字节后, SS 引脚必须切换先高然后低。此外,如果从机将数据写入SPI数据寄存器(SPDR)时,如果SS为低电位,则会发生写冲突错误。当CPHA = 1,采样边沿位于SPCLK时钟的第二个边沿。从机使用的第一个SPCLK时钟转移的MSB,而不是SS的下降沿。因此,在每次成功传输时SS 可以始终保持低电位保持低之间的转移。此格式更适合单主机单从机的结构使用。CPHA =1模式,从机的SS可以不连接在SPI系统中,直接接地。

在SPI传输使能(SPIEN = 1)前,必须先对SPI传输进行配置,否则传输过程中对LSBFE, MSTR, CPOL, CPHA及 SPR[1:0] 的任一更改,将会停止SPI传输并强迫总线进入空闲模式。所以在任何配置位更改前,请先关闭SPIEN使能位。

从机选择引脚SS配置

N76E003SPI提供灵活的SS 配置用于不同系统。当作为从机时, SS 始终定义为选择输入脚。当作为主机时,

SS有三种不同的功能定义,可以通过DISMODF (SPSR.3) 和SSOE (SPCR.7)来配置。默认情况DISMODF=0,

故障侦测功能打开, SS 配置为输入脚并检测是否发生故障。反之,如果DISMODF=1,故障侦测功能关闭,

SSOE寄存器定义控制SS 管脚。当SSOE=1,从机选择信号自动生成,主机的SS 管脚直接与从机的SS 脚连

接,当选择外部从机进行传输时SS 自动拉低,当进入闲置状态或者没有选择从机时,自动拉高。当SSOE=0且

DISMODF=1时,SS不再用作SPI管脚,而完全配置为普通端口状态。

模式故障侦测

在一个SPI网络中,当不止一个设备有可能成为主机时,为减少数据传输错误,模式故障侦测功能是非常有用

的。当一个主机打开模式故障侦测并发现SS 由其它设备拉低,配置详见 表14-1.从机选择脚定义,说明系统上

有一个从机试图寻找主机地址并把主机认为从机。此时,硬件会自动将SPCR 的 MSTR 和SPIEN清除,从而SPI

功能关闭,并使能错误侦测标志MODF (SPSR.4)置1 ,如果之前已打开中断ESPI (EIE .6) 和EA置1,则会进入

中断向量。

写冲突错误

SPI在发送方向上是单缓存,但在接收上是双缓存。除非前一个数据传输完,否则新的数据不能写入移位寄存

器。当正在进行一次传送时,如果设备同时又写数据到SPDR,将发生写冲突错误。发送数据时由于SPDR不是

一个双缓存,任何写入SPDR数据将直接写入SPI的移位寄存器。一旦发生一个写冲突错误,WCOL(SPSR.6)会

被硬件置1指示发生一个写冲突。这种情况下,当前的传输继续不停,然而引起写冲突的新数据将丢失。尽管

SPI逻辑可以在主机和从机之间进行写冲突检测,但写冲突通常会是一个从机错误,原因是当主机开始一次传送

时,从机是无法预知。在从机接收过程中,写SPDR也将产生写冲突错误。WCOL标志用软件清除。

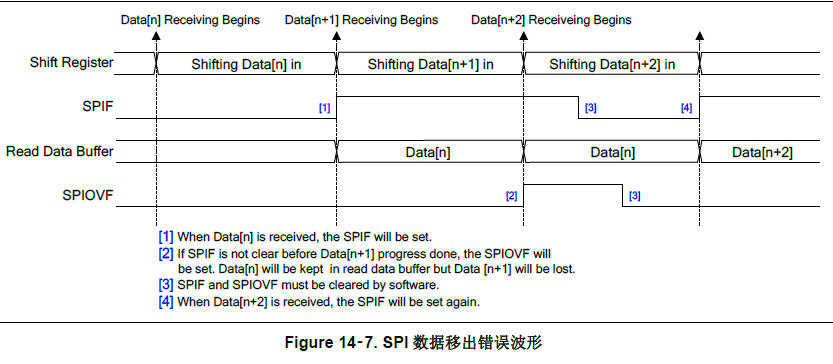

移出错误

对于接收数据,SPI是双缓存的。接收到的数据移入到一个读数据缓存中,同时能接收第二个数据。然而,在下

一个数据移入之前,必须确保已从SPDR中读取出已接收数据。在下一个数据被移入前,要把前一个数据从读缓

冲区内读出,并且清除SPIF,这样的才不会产生移出错误,反之,将产生移出错误。这种情况下,第二个字节

的数据不会正常移入读数据缓存,缓存区内仍保留有前一个数据。当发生移出错误时,SPIOVF (SPSR.5)会被

硬件置1。如果中断打开,会进入中断请求。Figure 14?7.表示接收数据与移出错误之间的关系。

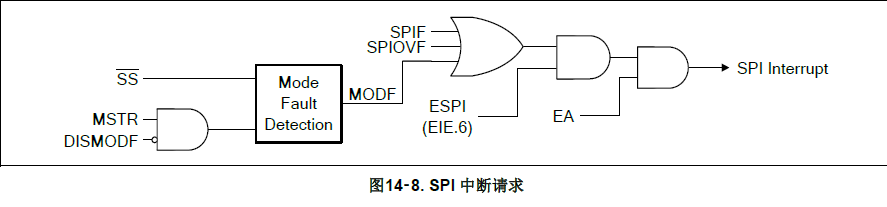

SPI 中断

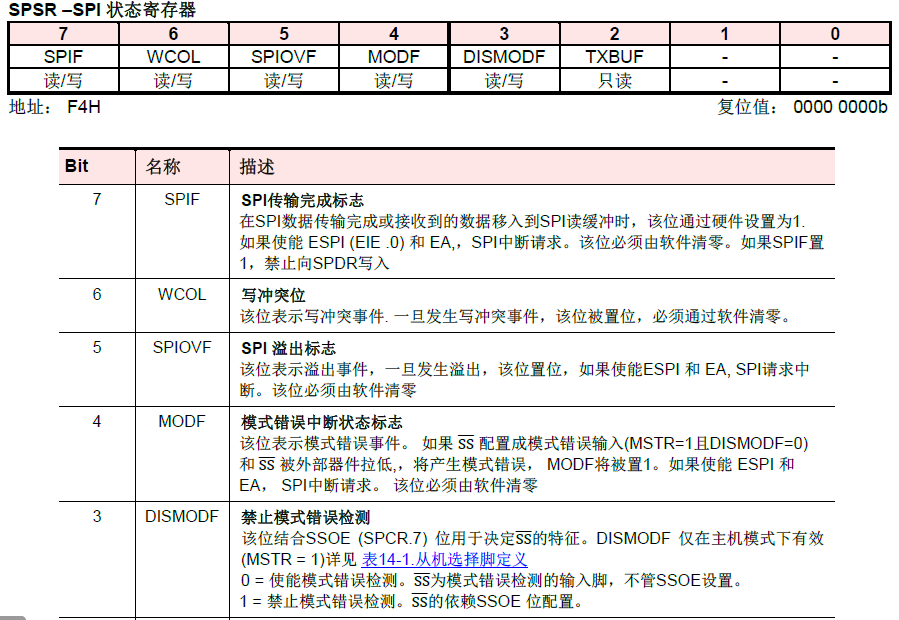

SPI中断状态标志包括SPIF、MODF 和 SPIOVF,用于产生SPI事件中断请求。这些位都放在SPSR寄存器中。

当有外部数据传入SPDR或自身完成数据传输后,SPIF标志将被置位。MODF置1时,表示SS 进入模式错误状

态,SPIOVF表示接收发生数据移出错误。当SPI中断打开时(ESPI (EIE.6) 和EA置1),当这3个标志中的任意

一个置1,CPU会执行SPI中断服务程序。用户若需要了解是由何种标志引起中断,必须检查相应的标志位。这

三个标志必须由用户软件清除。

/*---------------------------------------------------------------------------------------------------------*/ /* */ /* Copyright(c) 2015 Nuvoton Technology Corp. All rights reserved. */ /* */ /*---------------------------------------------------------------------------------------------------------*/ //*********************************************************************************************************** // Nuvoton Technoledge Corp. // Website: http://www.nuvoton.com // E-Mail : MicroC-8bit@nuvoton.com // Date : Apr/21/2015 //*********************************************************************************************************** //*********************************************************************************************************** // File Function: N76E885 Access SPI Flash (W25Q16BV) demo code //*********************************************************************************************************** #include <stdio.h> #include <intrins.h> #include <string.h> #include "N76E885.h" #include "Version.h" #include "Typedef.h" #include "Define.h" #include "SFR_Macro.h" #include "Common.h" #include "Delay.h" /* //-------- <<< Use Configuration Wizard in Context Menu >>> ------------ // //<e0> System Clock Source Configuration // <o1> System Clock Source Selection // <0=> 2~25MHz XTAL // <1=> 32.768KHz XTAL // <2=> 22.1184MHz Internal // <3=> 10KHz Internal // <4=> OSC-In External //</e> // //<e2> Clock Divider Configuration // <o3.0..7> System Clock Source Devider <1-255> // <i> Fsys = (System Clock Source) / (2 * Devider) //</e> // // <o4> SPI Clock Rate Selection (11.0592MHz System Clock) // <0=> 2.7648MHz, Fosc/4 // <1=> 1.3824MHz, Fosc/8 // <2=> 0.6912MHz, Fosc/16 // <3=> 0.3456MHz, Fosc/32 //-------- <<< end of configuration section >>> ------------------------------ */ #define SYS_CLK_EN 0 #define SYS_SEL 2 #define SYS_DIV_EN 0 //0: Fsys=Fosc, 1: Fsys = Fosc/(2*CKDIV) #define SYS_DIV 1 #define SPI_CLOCK 0 #define SS_PIN P04 #define WRITE_ENABLE 0x06 #define WRITE_DISABLE 0x04 #define READ_DATA 0x03 #define PAGE_PROGRAM 0x02 #define CHIP_ERASE 0xC7 #define READ_STATUS1 0x05 bit BIT_TMP; //----------------------------------------------------------------------------------------------------------- void SPI_Error(void) { printf ("\n* SPI Error, please check the connection between MCU and SPI Flash"); while(1); } //----------------------------------------------------------------------------------------------------------- void SPI_Initial(void) { #if SPI_CLOCK == 0 clr_SPR1; clr_SPR0; #elif SPI_CLOCK == 1 clr_SPR1; set_SPR0; #elif SPI_CLOCK == 2 set_SPR1; clr_SPR0; #elif SPI_CLOCK == 3 set_SPR1; set_SPR0; #endif /* /SS General purpose I/O ( No Mode Fault ) */ set_DISMODF; clr_SSOE; /* SPI in Master mode */ set_MSTR; /* MSB first */ clr_LSBFE; clr_CPOL; clr_CPHA; /* Enable SPI function */ set_SPIEN; } //----------------------------------------------------------------------------------------------------------- void Read_MID_DID(UINT8 *pu8MID,UINT8 *pu8DID) { SS_PIN = 0; SPDR = 0x90; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0xFF; while((SPSR&0x80)==0x00); *pu8MID = SPDR; clr_SPIF; SPDR = 0xFF; while((SPSR&0x80)==0x00); *pu8DID = SPDR; clr_SPIF; SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void Flash_Write_Enable(void) { SS_PIN = 0; SPDR = WRITE_ENABLE; while((SPSR&0x80)==0x00); clr_SPIF; SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void Flash_Write_Disable(void) { SS_PIN = 0; SPDR = WRITE_DISABLE; while((SPSR&0x80)==0x00); clr_SPIF; SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void Flash_Chip_Erase(void) { SS_PIN = 0; SPDR = CHIP_ERASE; while((SPSR&0x80)==0x00); clr_SPIF; SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void Flash_Read_Status(void) { UINT8 u8Status; SS_PIN = 0; do{ SPDR = READ_STATUS1; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0xFF; while((SPSR&0x80)==0x00); u8Status = SPDR; clr_SPIF; }while((u8Status&0x01)==0x01); SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void Flash_Erase_Verify(void) { UINT16 u16CNT; UINT8 u8Data; SS_PIN = 0; SPDR = READ_DATA; while((SPSR&0x80)==0x00); clr_SPIF; /* 24-bit Address */ SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; for(u16CNT=0;u16CNT<256;u16CNT++) { SPDR = 0x00; while((SPSR&0x80)==0x00); u8Data = SPDR; clr_SPIF; if(u8Data != 0xFF) { SPI_Error(); } } SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void Flash_Program(void) { UINT16 u16CNT; SS_PIN = 0; SPDR = PAGE_PROGRAM; while((SPSR&0x80)==0x00); clr_SPIF; /* 24-bit Address */ SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; /* Send the data to SPI_Flash buffer */ for(u16CNT=0;u16CNT<256;u16CNT++) { SPDR = (UINT8)u16CNT; while((SPSR&0x80)==0x00); clr_SPIF; } SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void Flash_Program_Verify(void) { UINT16 u16CNT; UINT8 u8Data; SS_PIN = 0; SPDR = READ_DATA; while((SPSR&0x80)==0x00); clr_SPIF; /* 24-bit Address */ SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; SPDR = 0x00; while((SPSR&0x80)==0x00); clr_SPIF; for(u16CNT=0;u16CNT<256;u16CNT++) { SPDR = 0x00; while((SPSR&0x80)==0x00); u8Data = SPDR; clr_SPIF; if(u8Data != (UINT8)u16CNT) { SPI_Error(); } } SS_PIN = 1; } //----------------------------------------------------------------------------------------------------------- void main(void) { UINT8 u8MID,u8DID; /* Note MCU power on system clock is HIRC (22.1184MHz), so Fsys = 22.1184MHz */ Set_All_GPIO_Quasi_Mode(); InitialUART0_Timer1_Type1(9600); /* 9600 Baud Rate*/ Show_FW_Version_Number_To_PC(); printf ("\n*==================================================================="); printf ("\n* Name: N76E885 SPI Demo Code, MCU <--> W25Q16BV"); printf ("\n*===================================================================\n"); /* Change system closk source */ #if SYS_CLK_EN == 1 #if SYS_SEL == 0 System_Clock_Select(E_HXTEN); //Fosc = 2~25MHz XTAL #elif SYS_SEL == 1 System_Clock_Select(E_LXTEN); //Fosc = 32.768KHz XTAL #elif SYS_SEL == 2 System_Clock_Select(E_HIRCEN); //Fosc = 22.1184MHz Internal RC #elif SYS_SEL == 3 System_Clock_Select(E_LIRCEN); //Fosc = 10KHz Internal RC #elif SYS_SEL == 4 System_Clock_Select(E_OSCEN); //Fosc = OSC-In External OSC #endif #endif #if SYS_DIV_EN == 1 CKDIV = SYS_DIV; //Fsys = Fosc / (2* CLKDIV) = Fcpu #endif SPI_Initial(); Read_MID_DID(&u8MID,&u8DID); printf ("\n* MID value of W25Q16BV = 0x%X",(UINT16)u8MID); printf ("\n* DID value of W25Q16BV = 0x%X",(UINT16)u8DID); if((u8MID != 0xEF)&&(u8DID != 0x17)) { SPI_Error(); } /* The procedure of SPI Flash at erase mode */ Flash_Write_Enable(); Flash_Chip_Erase(); Flash_Read_Status(); Flash_Write_Disable(); Flash_Erase_Verify(); /* The procedure of SPI Flash at program mode */ Flash_Write_Enable(); Flash_Program(); Flash_Read_Status(); Flash_Write_Disable(); /* Program verify */ Flash_Program_Verify(); printf("\nFinished the SPI Demo Code and test pass!!!\n"); while(1); } //-----------------------------------------------------------------------------------------------------------

具体讲解 容后再说