您好,欢迎进入江南娱乐手机客户端 官方网站!

您好,欢迎进入江南娱乐手机客户端 官方网站!

2006年ARM公司推出了基于ARMV7架构的cortex系列的标准体系结构,以满足各种技术得不同性能要求,包含了A,R,M三个分工明确的系列

其中A系列面向复杂的尖端应用程序,用于运行开放式的复杂操作系统;R系列适合实时操作系统,M系列专门针对低成本的微控制领域。而我们今天要学习的STM32就是M3的处理器

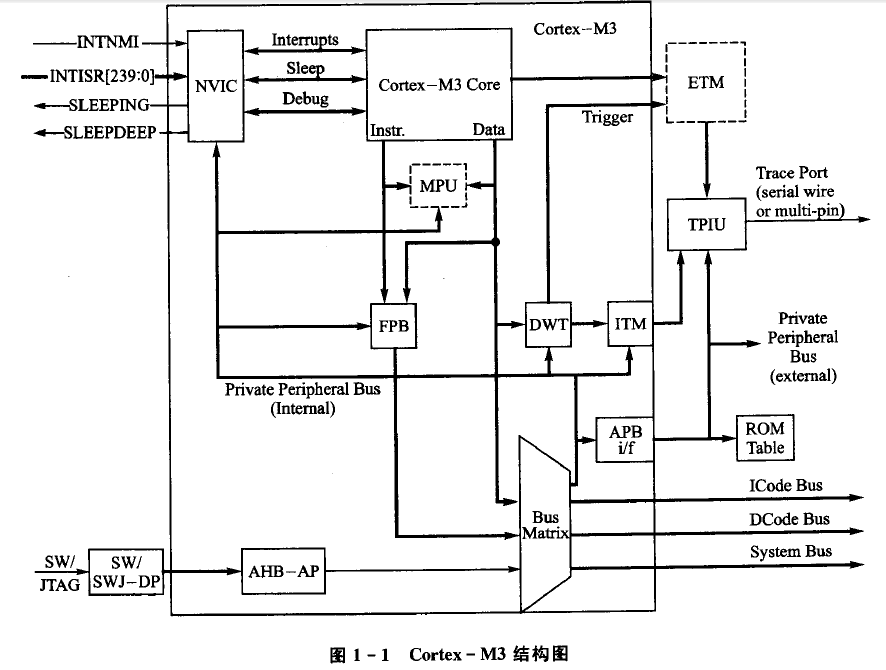

STM32(M3)处理器的基本结构,基本结构如图所示,主要包括处理器核cortex-m3 core,NVIC,BUS MATRIS,FLASH转换,及断点单元,DWT,ITM,MPU,ETM,TPIU,ROM Table

SW/SWJ-DP等模块,其中MPU和ETM单元是可选单元。

这些单元可分为内外两个层次,其中ETM,TPIU,ROM Table,SW/SWJ-DP单元属于外层,因为这四个单元或可选或可灵活配置实现,也就是在处理器具体实现时TPIU,ROM Table

,SW/SWJ-DP可能与图1-1可能不同,

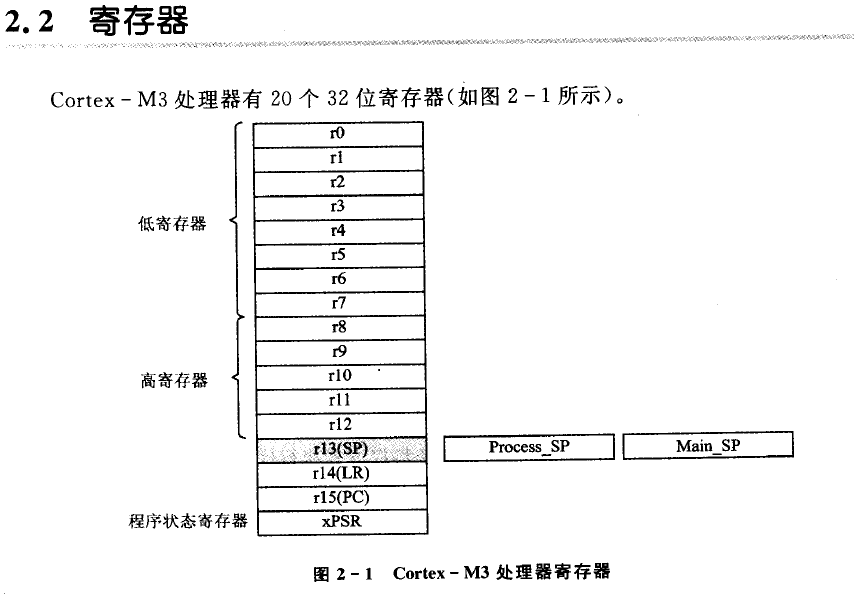

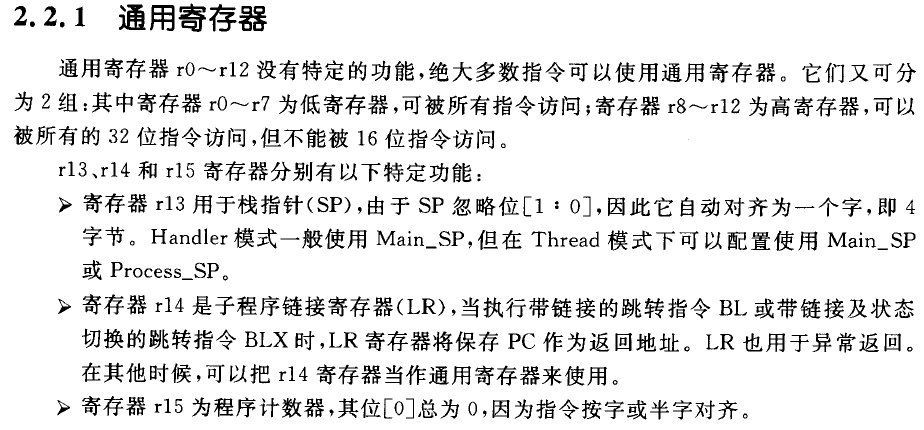

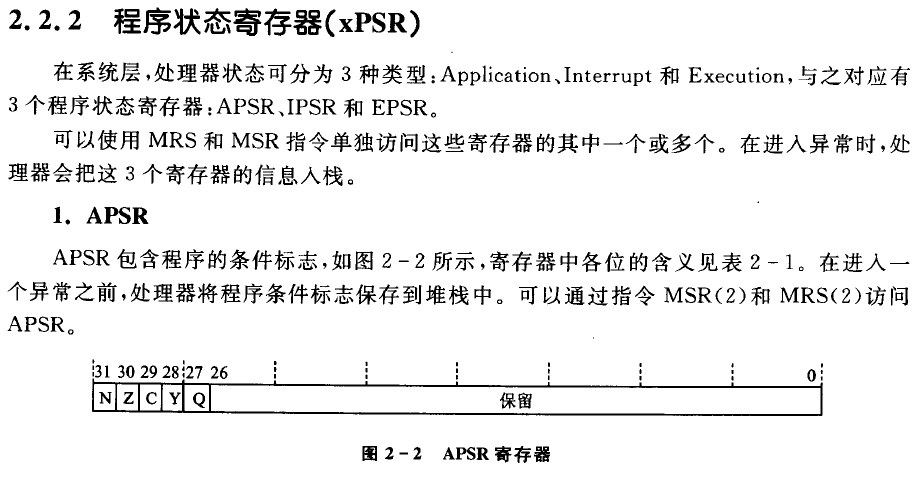

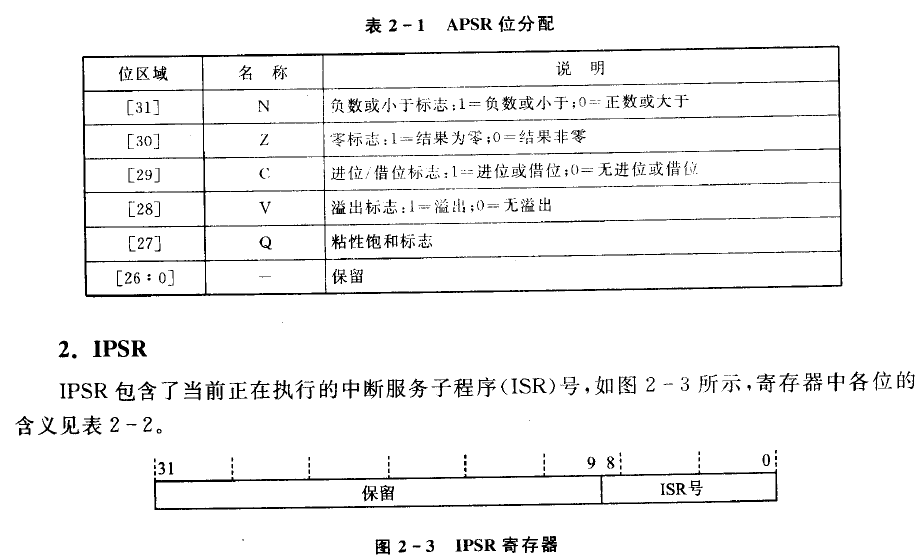

cortex-m3核内部寄存器包括:13个通用32位寄存器,连接寄存器LR,程序计数器PC,程序状态寄存器 xpsr和2个堆栈指针寄存器;

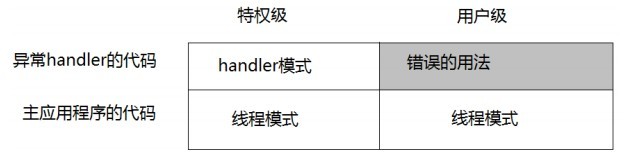

Cortex-M3处理器支持两种处理器的操作模式,还支持两级特权操作。

两种操作模式分别为:处理者模式和线程模式(thread mode)。

引入两个模式的本意,是用于区别普通应用程序的代码和异常服务例程的代码——包括中断服务例程的代码。

两级特权操作分别为:特权级和用户级。

这可以提供一种存储器访问的保护机制,使得普通的用户程序代码不能意外地,甚至是恶意地执行涉及到要害的操作。

处理器支持两种特权级,这也是一个基本的安全模型。

主应用程序(线程模式),既可以使用特权级,也可以使用用户级;

异常服务例程(处理者模式)必须在特权级下执行。

通过引入特权级和用户级,就能够在硬件水平上限制某些不受信任的或者还没有调试好的程序,

不让它们随便地配置涉及要害的寄存器,因而系统的可靠性得到了提高。