将CPU与内存分开并非十全十美,反而会导致所谓的冯·诺伊曼瓶颈(von Neumann bottleneck):在CPU与内存之间的流量(资料传输率)与内存的容量相比起来相当小,在现代电脑中,流量与CPU的工作效率相比之下非常小,在某些情况下(当CPU需要在巨大的资料上执行一些简单指令时),资料流量就成了整体效率非常严重的限制。CPU将会在资料输入或输出内存时闲置。由于CPU速度以及内存容量的成长速率远大于双方之间的流量,因此瓶颈问题越来越严重。而冯·诺伊曼瓶颈是约翰·巴科斯在1977年ACM图灵奖得奖致词时第一次出现,根据巴科斯所言:

“……确实有一个变更储存装置的方法,比借由冯·诺伊曼瓶颈流通大量资料更为先进。瓶颈这词不仅是对于问题本身资料流量的叙述,更重要地,也是个使我们的思考方法局限在‘一次一字符’模式的智能瓶颈。它使我们怯于思考更广泛的概念。因此编程成为一种计划与详述通过冯·诺伊曼瓶颈的字符资料流,且大部分的问题不在于资料的特征,而是如何找出资料。”

在CPU与内存间的快取内存抒解了冯·诺伊曼瓶颈的效能问题。另外,

分支预测(branch predictor)算法的建立也帮助缓和了此问题。巴科斯在1977年论述的“智能瓶颈”已改变甚多。且巴科斯对于此问题的解决方案并没有造成明显影响。现代的

函数式编程以及面向对象编程已较少执行如早期Fortran一般会“将大量数值从内存搬入搬出的操作”,但平心而论,这些操作的确占用电脑大部分的执行时间。

结构

1945年,

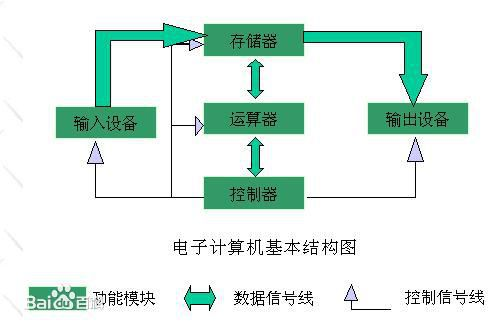

冯·诺依曼首先提出了“存储程序”的概念和

二进制原理,后来,人们把利用这种概念和原理设计的电子计算机系统统称为“冯·诺依曼型结构”计算机。冯·诺依曼结构的处理器使用同一个存储器,经由同一个总线传输。

冯·诺曼结构处理器具有以下几个特点:必须有一个存储器;必须有一个控制器;必须有一个运算器,用于完成算术运算和逻辑运算;必须有输入和输出设备,用于进行人机通信。

哈佛结构

哈佛结构是一种将程序指令存储和

数据存储分开的存储器结构。

中央处理器首先到程序指令存储器中读取程序指令内容,解码后得到数据地址,再到相应的数据存储器中读取数据,并进行下一步的操作(通常是执行)。程序指令存储和数据存储分开,可以使指令和数据有不同的数据宽度,如Microchip公司的PIC16芯片的程序指令是14位宽度,而数据是8位宽度。

哈佛结构的微处理器通常具有较高的执行效率。其程序指令和数据指令分开组织和存储的,执行时可以预先读取下一条指令。使用哈佛结构的中央处理器和微控制器有很多,除了上面提到的Microchip公司的PIC系列芯片,还有

摩托罗拉公司的MC68系列、Zilog公司的Z8系列、

ATMEL公司的AVR系列和ARM公司的ARM9、ARM10和ARM11。

哈佛结构是指程序和数据空间独立的体系结构,目的是为了减轻程序运行时的访存瓶颈。

例如最常见的卷积运算中, 一条指令同时取两个

操作数, 在流水线处理时, 同时还有一个取指操作,如果程序和数据通过一条总线访问,取指和取数必会产生冲突,而这对大运算量的循环的执行效率是很不利的。哈佛结构能基本上解决取指和取数的冲突问题。而对另一个操作数的访问,就只能采用Enhanced哈佛结构了,例如像TI那样,数据区再split,并多一组总线。或向AD那样,采用指令cache,指令区可存放一部分数据。

在

DSP算法中,最大量的工作之一是与存储器交换信息,这其中包括作为输入信号的

采样数据、滤波器系数和程序指令。例如,如果将保存在存储器中的2个数相乘,就需要从存储器中取3个

二进制数,即2个要乘的数和1个描述如何去做的程序指令。DSP内部一般采用的是

哈佛结构,它在片内至少有4套总线:程序的

数据总线,程序的

地址总线,数据的数据总线和数据的地址总线。这种分离的程序总线和数据总线,可允许同时获取

指令字(来自

程序存储器)和

操作数(来自数据存储器),而互不干扰。这意味着在一个

机器周期内可以同时准备好指令和操作数。有的DSP芯片内部还包含有其他总线,如DMA总线等,可实现单周期内完成更多的工作。这种多

总线结构就好像在DSP内部架起了四通八达的高速公路,保障运算单元及时地取到需要的数据,提高运算速度。因此,对DSP来说,

内部总线是个资源,总线越多,可以完成的功能就越复杂。超级哈佛结构(superHarvard architecture,缩写为SHARC),它在哈佛结构上增加了指令cache(

缓存)和专用的I/O控制器。

哈佛结构处理器有两个明显的特点:使用两个独立的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存;使用独立的两条总线,分别作为CPU与每个存储器之间的专用通信路径,而这两条总线之间毫无关联。

改进的哈佛结构,其结构特点为:以便实现

并行处理;具有一条独立的

地址总线和一条独立的

数据总线,利用公用地址总线访问两个存储模块(程序存储模块和

数据存储模块),公用数据总线则被用来完成程序存储模块或数据存储模块与CPU之间的数据传输。

两者区别

冯·诺依曼理论的要点是:数字计算机的数制采用二进制;计算机应该按照程序顺序执行。人们把

冯诺依曼的这个理论称为

冯诺依曼体系结构。从ENIAC到当前最先进的计算机都采用的是冯诺依曼体系结构。所以冯诺依曼是当之无愧的数字计算机之父。

根据冯诺依曼体系结构构成的计算机,必须具有如下功能:把需要的程序和数据送至计算机中;必须具有长期记忆程序、数据、中间结果及最终运算结果的能力;能够完成各种算术、逻辑运算和数据传送等数据加工处理的能力;能够根据需要控制程序走向,并能根据指令控制机器的各部件协调操作;能够按照要求将处理结果输出给用户。

哈佛结构是为了高速数据处理而采用的,因为可以同时读取指令和数据(分开存储的)。大大提高了

数据吞吐率,缺点是结构复杂。通用微机指令和数据是混合存储的,结构上简单,成本低。假设是哈佛结构:你就得在电脑安装两块硬盘,一块装程序,一块装数据,内存装两根,一根储存指令,一根存储数据……

是什么结构要看

总线结构的。51单片机虽然数据指令存储区是分开的,但总线是

分时复用的,所以顶多算改进型的

哈佛结构。ARM9虽然是哈佛结构,但是之前的版本也还是冯·诺依曼结构。早期的X86能迅速占有市场,一条很重要的原因,正是靠了

冯·诺依曼这种实现简单,成本低的总线结构。处理器虽然

外部总线上看是诺依曼结构的,但是由于内部CACHE的存在,因此实际上内部来看已经算是改进型哈佛结构的了。至于优缺点,哈佛结构就是复杂,对

外围设备的连接与处理要求高,十分不适合外围存储器的扩展。所以早期通用CPU难以采用这种结构。而

单片机,由于内部集成了所需的存储器,所以采用哈佛结构也未尝不可。处理器,依托CACHE的存在,已经很好的将二者统一起来了。

哈佛体系架构有个致命的弱点在动态加载程序上面,想象我们从外存中读取一段程序然后加载到RAM,这个程序是在数据内存当中的,我们需要一种机制将数据内存再传输到程序内存当中去,这反而增加了设备复杂度。另外,绝对不允许CPU/DSP读取程序内存来当作数据,这也是不现实的,程序一般都有只读数据区和静态数据区,烧写程序的时候会当作程序的一部分烧进ROM中,想像一下如果为了把程序和数据分开,而需要设置两块ROM,再把其中一块ROM和RAM通过复用器接起来,这是多么惨烈的景象,更不用说每次烧写都要分开烧两块ROM了。实际上即使是DSP通常也允许从程序内存的总线上读取一些数据。

对于多任务操作系统来说,管理程序内存是一件非常重要的事情,而且仅仅是保护模式下的页面映射等等机制就已经足够复杂了,如果还要求将程序和数据分开管理,复杂度就太高了。这种时候冯诺依曼体系结构就有非常大的优势了。纯的(或者接近纯的)哈佛结构只用于非常简单的硬件系统,这种系统当中通常程序完全运行在ROM中,数据几乎完全存储于RAM中,这样的结构足够简单。而要支持多任务的处理器通常引入Cache层,在Cache层实现一个哈佛体系架构,这样可以兼顾性能和灵活性。

转自知乎 链接:https://www.zhihu.com/question/22406681/answer/109474052

实际上,绝大多数现代计算机使用的是所谓的“Modified Harvard Architecture”,指令和数据共享同一个 address space,但缓存是分开的。可以说是两种架构的一种折中吧。

在现实世界中很少有非常纯粹的概念,特别是在实际的应用里。教科书里的大多是理想化的模型,便于掌握某个概念的重点和本质,但实际中很难达到这种理想化的状态。

哈佛结构和冯诺依曼结构主要区别在是否区分指令与数据。在教科书里这是两种截然不同的做法。

实际上在内存里,指令和数据是在一起的。而在CPU内的缓存中,还是会区分指令缓存和数据缓存,最终执行的时候,指令和数据是从两个不同的地方出来的。你可以理解为在CPU外部,采用的是冯诺依曼模型,而在CPU内部用的是哈佛结构。

大部分的DSP都没有缓存,因而直接就是哈佛结构。

哈佛结构设计复杂,但效率高。冯诺依曼结构则比较简单,但也比较慢。CPU厂商为了提高处理速度,在CPU内增加了高速缓存。也基于同样的目的,区分了指令缓存和数据缓存。有时为了解决现实问题,究竟是什么主义真的没那么重要。因而个人认为争论到底是哪种结构意义不大。

转自知乎 链接:https://www.zhihu.com/question/22406681/answer/21264994